Материалы по тегу: dpu

|

29.05.2023 [07:30], Сергей Карасёв

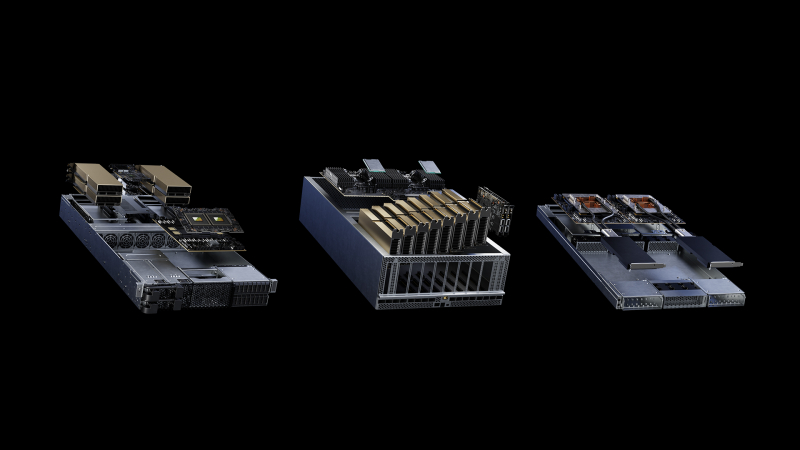

NVIDIA представила модульную архитектуру MGX для создания ИИ-систем на базе CPU, GPU и DPUКомпания NVIDIA на выставке Computex 2023 представила архитектуру MGX, которая открывает перед разработчиками серверного оборудования новые возможности для построения HPC-систем, платформ для ИИ и метавселенных. Утверждается, что MGX закладывает основу для быстрого создания более 100 вариантов серверов при относительно небольших затратах. Концепция MGX предусматривает, что разработчики на первом этапе проектирования выбирают базовую системную архитектуру для своего шасси. Далее добавляются CPU, GPU и DPU в той или иной конфигурации для решения определённых задач. Таким образом, на базе MGX может быть построена серверная система для уникальных рабочих нагрузок в области наук о данных, больших языковых моделей (LLM), периферийных вычислений, обработки графики и видеоматериалов и пр. Говорится также, что благодаря гибридной конфигурации на одной машине могут выполняться задачи разных типов, например, и обучение ИИ-моделей, и поддержание работы ИИ-сервисов. Одними из первых системы на архитектуре MGX выведут на рынок компании Supermicro и QCT. Первая предложит решение ARS-221GL-NR с NVIDIA Grace, а вторая — сервер S74G-2U на базе NVIDIA GH200 Grace Hopper. Эти платформы дебютируют в августе нынешнего года. Позднее появятся MGX-платформы ASRock Rack, ASUS, Gigabyte, Pegatron и других производителей. Архитектура MGX совместима с нынешним и будущим оборудованием NVIDIA, включая H100, L40, L4, Grace, GH200 Grace Hopper, BlueField-3 DPU и ConnectX-7. Поддерживаются различные форм-факторы систем: 1U, 2U и 4U. Возможно применение воздушного и жидкостного охлаждения.

11.05.2023 [01:38], Владимир Мироненко

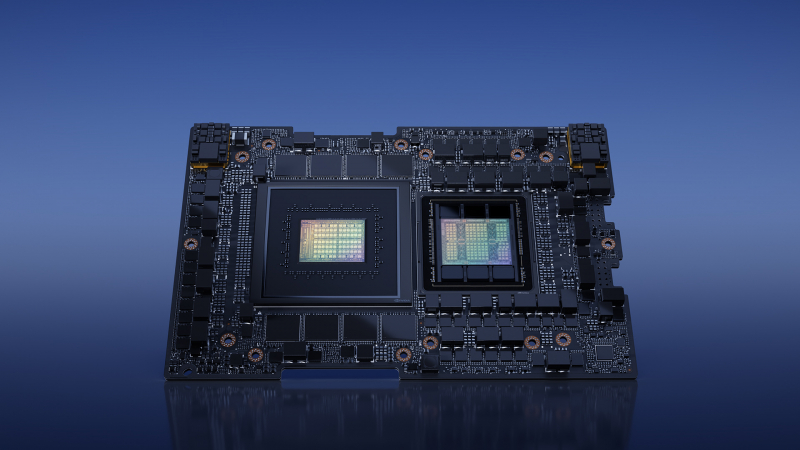

ИИ-суперкомпьютер для богатых: теперь в облаке Google Cloud можно получить сразу 26 тыс. ускорителей NVIDIA H100Компания Google Cloud представила на конференции для разработчиков Google I/O инстансы Google Compute Engine A3, специально созданные для обеспечения максимальной производительности рабочих нагрузок машинного обучения. Новинки используют современные CPU, быструю память, ускорители NVIDIA и IPU Intel. Виртуальная машина A3 включает:

Помимо того, что новые инстансы используют DPU/IPU Mount Evans, разработанные совместно с Intel, кластеры A3 также задействуют фирменные оптические коммутаторы Google Jupiter с возможность переконфигурации топологии по требованию, которые компания уже использует в кластерах с собственными ИИ-ускорителями. Всё это позволяет объединять до 26 тыс. ускорителей H100 в облачный ИИ-суперкомпьютер производительность до 26 Эфлопс (TF32). Ключевое отличие от других облачных предложений именно в интерконнекте и масштабируемости. Например, ИИ-суперкомпьютеры в Microsoft Azure объединяют тысячи и даже десятки тысяч ускорителей с использованием InfiniBand и DPU NVIDIA. В Oracle Cloud Infrastructure (OCI), где ранее был поставлен рекорд по объединению 32 768 ускорителей, используется тот же подход. Наконец, в AWS можно объединить до 20 тыс. ускорителей благодаря EFA. Google предложит клиентам несколько вариантов использования A3: клиенты смогут запускать ВМ самостоятельно или в качестве управляемого сервиса, где Google возьмёт на себя большую часть работы. Возможно использование A3 в Google Kubernetes Engine (GKE) или в Vertex AI. В настоящее время виртуальные машины A3 доступны только после регистрации в списке ожидания превью. Сейчас компания занята развёртыванием множественных кластеров A3 в наиболее крупных облачных регионах.

03.05.2023 [18:13], Сергей Карасёв

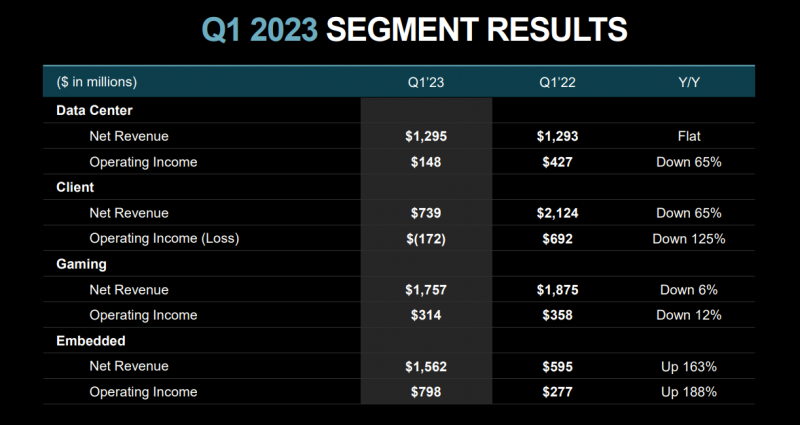

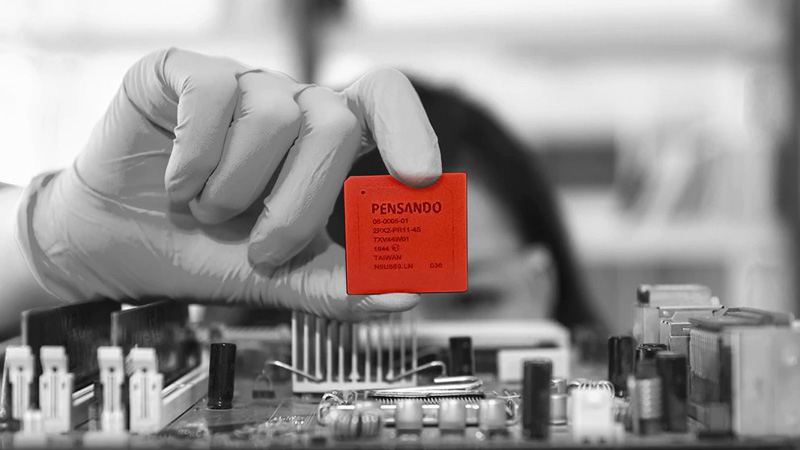

В не слишком удачном квартальном отчёте AMD отметила, что в облаке Microsoft Azure появились DPU Pensando, а серверные решения помогут ей заработать во втором полугодииКомпания AMD, по сообщению ресурса The Register, нашла крупного заказчика для DPU (Data Processing Unit) семейства Pensando: им стало облако Microsoft Azure. Доступ к этим специализированным ускорителям теперь предоставляется клиентам по модели «как услуга». Это тем более любопытно, что Microsoft недавно поглотила разработчика DPU Fungible. О поставках DPU Pensando в интересах Microsoft сообщила президент и исполнительный директор AMD Лиза Су (Lisa Su) в ходе оглашения финансовых показателей за I квартал 2023 года. Ускорители применяются в составе недавно анонсированной службы Microsoft Accelerated Connections. Гиперскейлеры зачастую используют DPU, но делают это для поддержания работы собственных сервисов. В случае Azure доступ к таким ускорителям предоставляется сторонним заказчикам.

Источник изображения: AMD В финансовом отчёте AMD говорится, что выручка по итогам I четверти 2023-го составила $5,35 млрд. Это примерно на 9 % меньше результата годичной давности, равнявшегося $5,89 млрд. Компания понесла чистые убытки в размере $139 млн, или 9 центов в пересчёте на одну ценную бумагу. Для сравнения: в I квартале 2022 года AMD продемонстрировала чистую прибыль на уровне $786 млн, или 56 центов на акцию. Выручка подразделения ЦОД за год практически не изменилась: она составила $1,30 млрд против $1,29 млрд в I четверти 2022-го. При этом операционная прибыль рухнула в годовом исчислении на 65 % — с $427 млн до $148 млн. По направлению встраиваемых систем квартальная выручка за год взлетела на 163 % — с $595 млн до $1,56 млрд. Операционная прибыль в этой группе поднялась на 188 %, достигнув $798 млн. По словам госпожи Су, AMD ожидает, что спрос на серверы во втором квартале 2023 года «остается смешанным». При этом компания рассматривает в качестве потенциальных областей роста ЦОД-сегмент и рынок встраиваемых систем. Увеличению продаж должно способствовать бурное развитие технологий ИИ. Компания ожидает, что на рынке будут востребованы процессоры Genoa и Bergamo, а также ускорители MI300 и решения Xilinx.

30.11.2022 [16:55], Алексей Степин

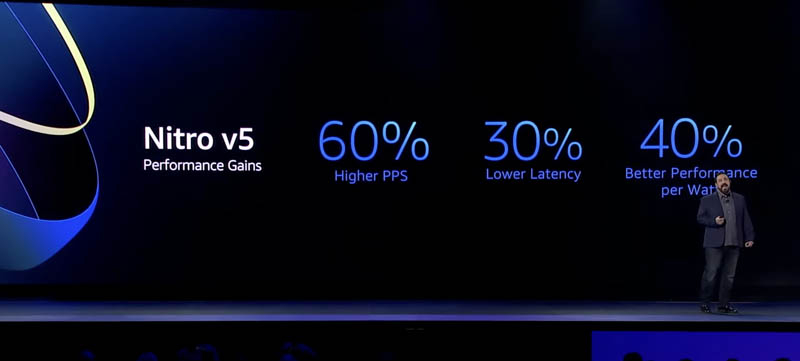

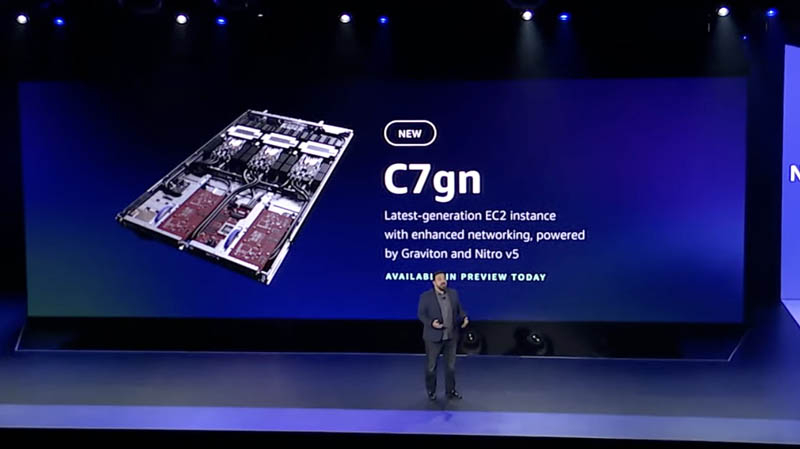

AWS представила пятое поколение аппаратных гипервизоров NitroНа днях крупный провайдер облачных услуг, компания Amazon Web Services представила новые варианты инстансов на базе новейших процессоров Graviton3E, но данный чип — не единственная новинка AWS. Одновременно с Graviton3E было представлено и пятое поколение аппаратных гипервизоров Nitro, существенно выигрывающих по ключевым показателям у решений предыдущего, четвёртого поколения.

Здесь и далее источник изображений: ServeTheHome Главная идея Nitro — сочетание «кремния» гипервизора, DPU и сопроцессора безопасности с поддержкой Root of Trust в едином чипе. В системах AWS плата с чипом Nitro полностью управляет распределением вычислительных ресурсов и памяти, избавляя от этой нагрузки хост-процессоры. По результатам тестов, проведённых AWS, производительность облачных инстансов с использованием ускорителей Nitro практически не отличается от производительности классической bare metal-системы.  AWS Nitro v5 использует кастомный кристалл, разработанный Annapurna Labs. По сравнению с Nitro v4, количество транзисторов было удвоено, но за счёт этого удалось на 60 % поднять скорость обработки сетевых пакетов, на 30 % снизить латентность, а также, благодаря продвинутому техпроцессу, обеспечить лучшую удельную производительность.

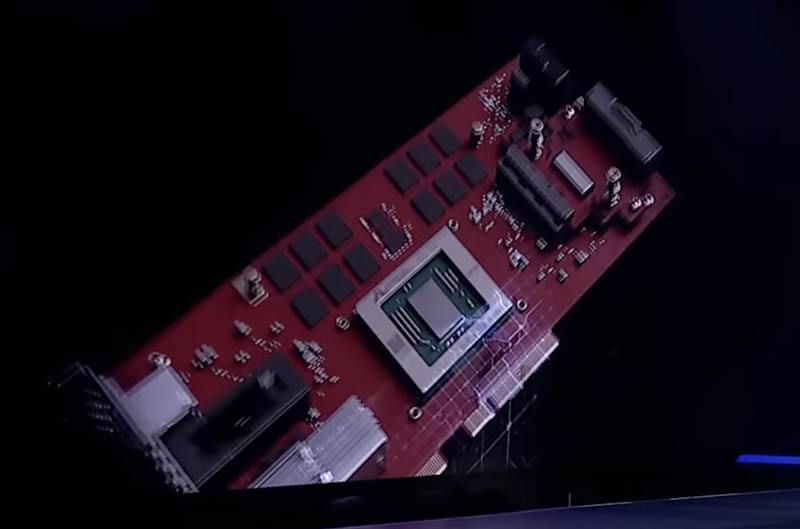

Платы AWS Nitro v5 используют проприетарные разъёмы Улучшились и другие характеристики: на 50 % выросла пропускная способность памяти и вдвое возросла производительность подсистемы PCI Express. Платы Nitro v5 станут сердцем новых инстансов C7gn, где обеспечат полную изоляцию критически важных подсистем, таких, как прошивки BIOS, BMC и накопителей от гостевого доступа извне и позволят обновлять эти прошивки без влияния на клиентские нагрузки.  Также они возьмут на себя обслуживание сетей VPC/EBS, включая переход на использование SRD вместо TCP, и накопителей Nitro SSD. AWS уже объявила о возможности предварительного тестирования систем C7gn на базе Nitro v5 и новейших процессоров Graviton3/3E.

28.04.2022 [22:54], Алексей Степин

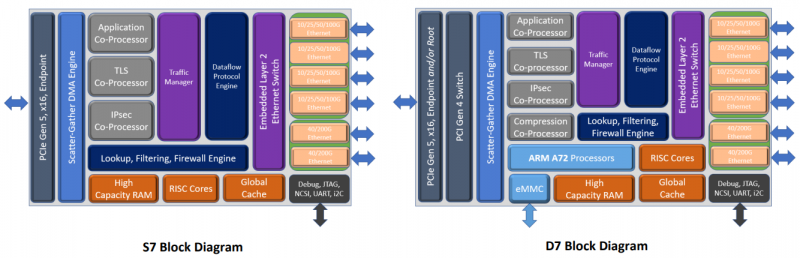

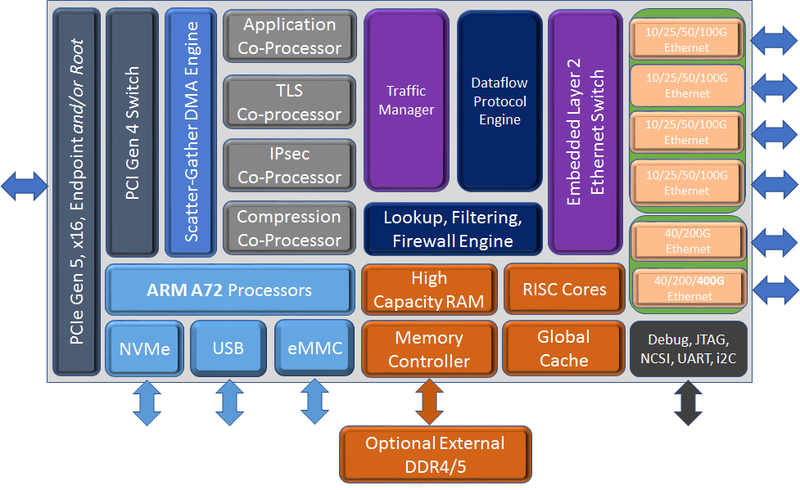

Chelsio представила седьмое поколение сетевых чипов Terminator: 400GbE и PCIe 5.0 x16Компания Chelsio Communications анонсировала седьмое поколение своих сетевых процессоров Terminator с поддержкой 400GbE. От предшественников T7 отличает более развитая вычислительная часть общего назначения, включающая в себя до 8 ядер Arm Cortex-A72, так что их уже можно назвать DPU. Всего представлено пять вариантов 5 чипов (T7, N7, D7, S74 и S72), которые различаются между собой набором движков и ускорителей. Референсная платформа T7 будет доступна в мае, первых же адаптеров на базе новых DPU следует ожидать в III квартале 2022 года. Для задач сжатия, дедупликации или криптографии есть отдельные сопроцессоры. Никуда не делся и привычный для серии Unified Wire встроенный L2-коммутатор. Для подключения к хосту T7 теперь использует шину PCIe 5.0 x16, причём он же содержит и root-комплекс. Более того, имеется и набортный коммутатор+мост PCIe 4.0, и NVMe-интерфейс, и даже поддержка эмуляции NVMe. Всё это, к примеру, позволяет легко и быстро создать NVMe-oF хранилище или мост NVMe-NVMe для компрессии и шифрования данных на лету. Новинка предлагает ускорение работы RoCEv2 и iWARP, FCoE и NVMe/TCP, iSCSI и iSER, а также RAID5/6. Сетевая часть поддерживает разгрузку Open vSwitch и Virt-IO.

Блок-схема старшего варианта T7 (Изображения: Chelsio Communcations) Впрочем, поддержки P4 тут нет — Chelsio продолжает использовать собственные движки для обработки трафика. Но наработки, сделанные для серий T5 и T6, будет проще перенести на новое поколение чипов. Кроме того, появилась и практически обязательная нынче «глубокая» телеметрия всего проходящего через DPU трафика для повышения управляемости и его защиты. Если и этого окажется мало, то к T7 (и D7) можно напрямую подключить FPGA, а набортную память расширить банками DDR4/5. В пресс-релизе также отмечается, что T7 сможет стать достойной заменой InfiniBand в HРC-системах. Вариант D7 наиболее близок к T7, но предлагает только 200GbE-подключение, лишён некоторых функций и второстепенных интерфейсов, да и в целом рассчитан на создание СХД. N7, напротив, лишён Arm-ядер и всех функций для работы с хранилищами, нет у него и PCIe-коммутатора и моста. Предлагает он только 200GbE-интерфейсы. Наконец, чипы серии S7 лишены целого ряда второстепенных функций и предоставляют только 100/200GbE-подключение. Они относятся скорее к SmartNIC, поскольку начисто лишены Arm-ядер и некоторых функций. Но зато они и недороги. Кроме того, в седьмом поколении Termintator появилась возможность обойтись без набортной DRAM с сохранением всей функциональности. Так что использование памяти хоста позволит дополнительно снизить стоимость конечных решений, которые будут создавать OEM-производители. Сами чипы производятся с использованием техпроцесса TSMC 12-нм FFC, так что даже у старшей версии чипов типовое энергопотребление не превышает 22 Вт.

19.12.2021 [18:06], Алексей Степин

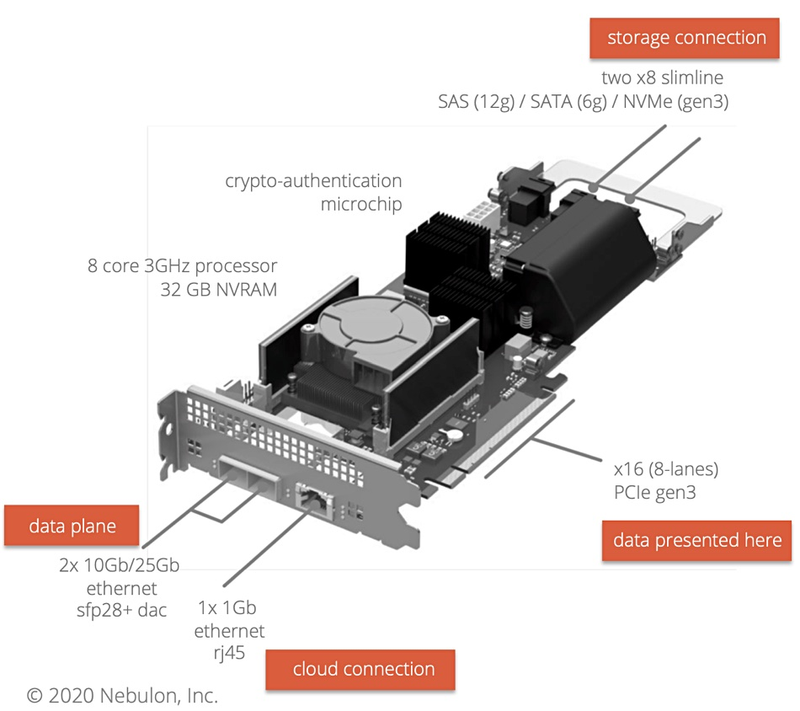

Nebulon поможет HCI-решениям освоить рынок периферийных вычисленийПо мере внедрения 5G-сетей объёмы данных, добываемых и обрабатываемых на периферии, будут только расти, и здесь новое решение Nebulon для микро-ЦОД окажется весьма к месту. Компания Nebulon была основана лишь 2018 году, а в 2020 году она представила свои первые решения, концептуально очень схожие с тем, что сейчас принято называть DPU. Изначально это были ускорители под названием SPU (Storage Processing Unit), однако впоследствии первое слово заменили на Service, поскольку речь шла уже об облачных системах, и данные платы стали частью того, что сама Nebulon называет «умной инфраструктурой» (Smart Infrastructure).

Nebulon SPU. Изображения: Nebulon Но у SPU нашлось и ещё одно применение, связанное с периферийной серверной инфраструктурой. Её особенности таковы, что требуют максимальной компактности оборудования, и это, по мнению Nebulon, затрудняет использование классических решений для гиперконвергентной инфраструктуры (HCI), поскольку, по словам Nebulon, она обычно для арбитража, который необходим для стабильности работы, требует наличия в системе минимум трёх узлов.  Такой «узел-арбитр» (quorum witness, QW) гарантирует бесперебойную работу системы в том случае, если какой-либо из её основных узлов испытывает проблемы с сетевым подключением. Но в условиях периферии третьему узлу бывает просто негде разместиться, а ведь нужен ещё и сетевой коммутатор. Тут-то на помощь и может прийти ускоритель Nebulon SPU, который можно назвать полноценным «сервером на плате»: он несёт на борту восьмиядерный CPU и 32 Гбайт DRAM. Основным интерфейсом SPU является PCIe 3.0 x16 (8 линий) + ещё два набора по 8 линий могут обслуживать NVMe SSD (но есть и поддержка SAS/SATA). С такой платой HCI-кластер может иметь в составе всего два узла. Коммутатор не требуется, поскольку плата располагает двумя портами 10/25GbE. Интеграцию такого HCI-кластера с облаком, автоматизацию и арбитраж посредством Nebulon ON также берёт на себя SPU. Компания-разработчик назвала данную технологию smartEdge.

29.10.2021 [02:28], Игорь Осколков

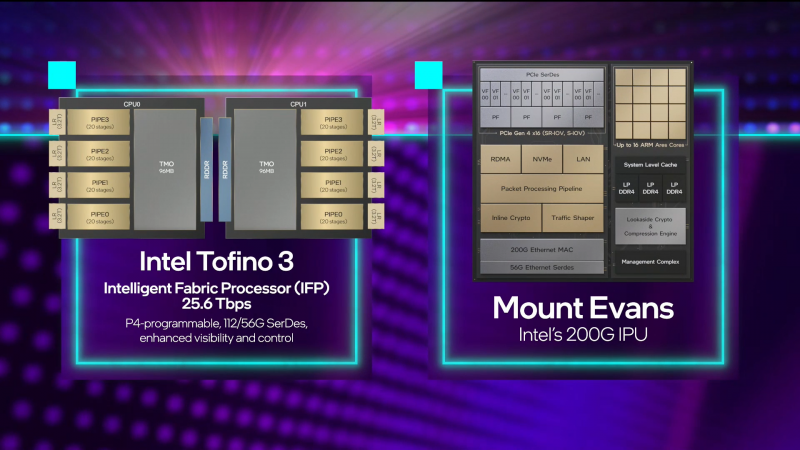

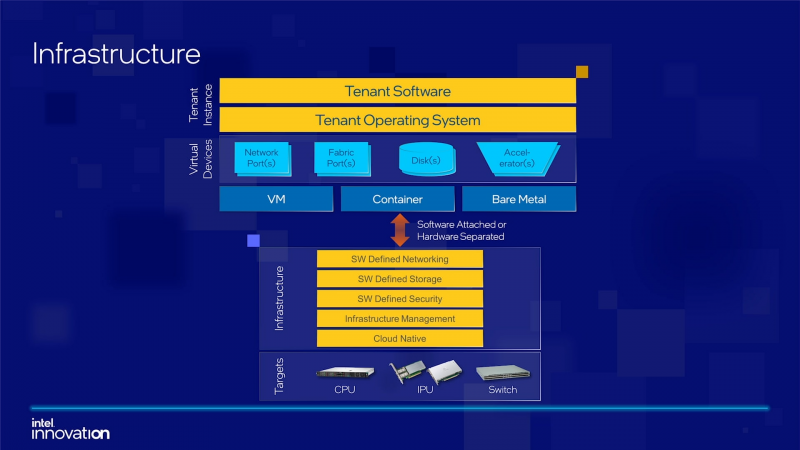

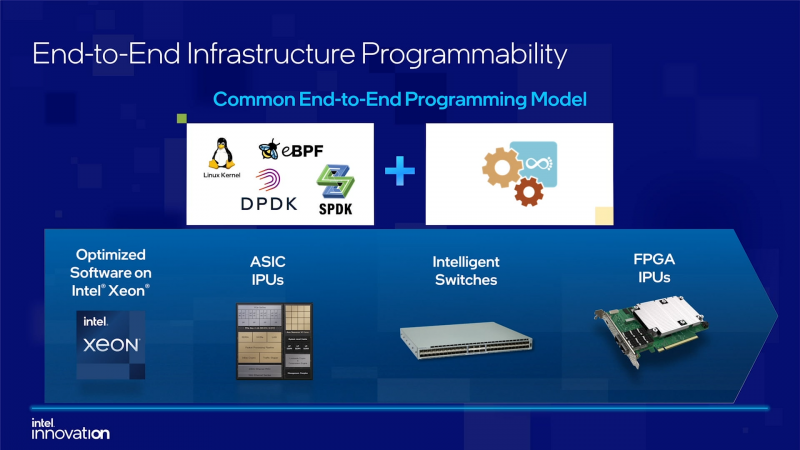

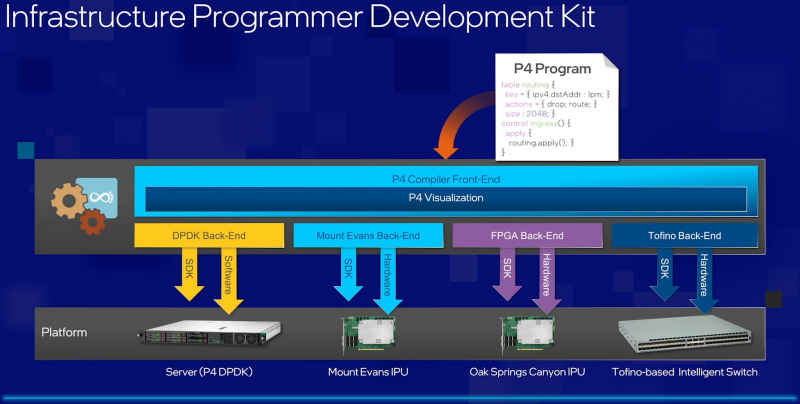

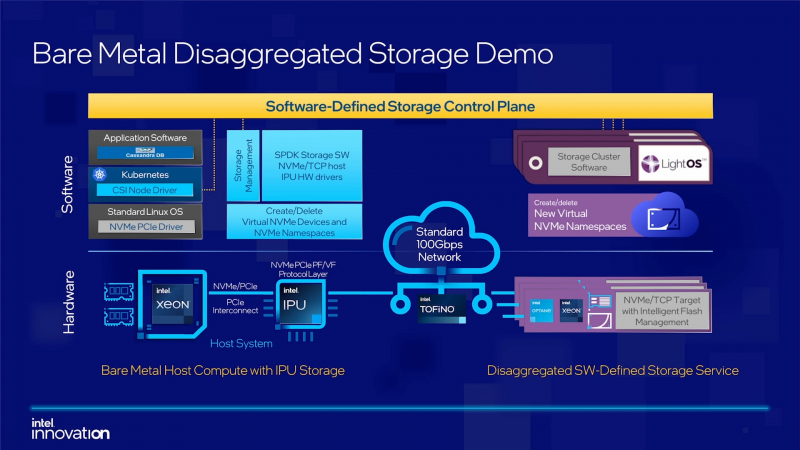

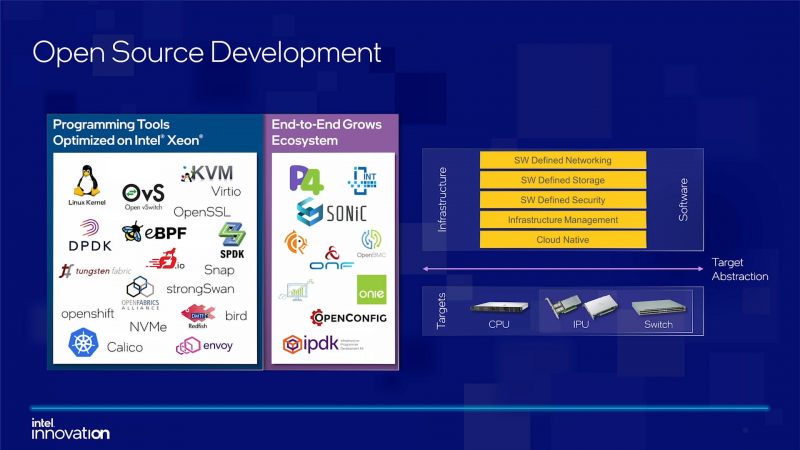

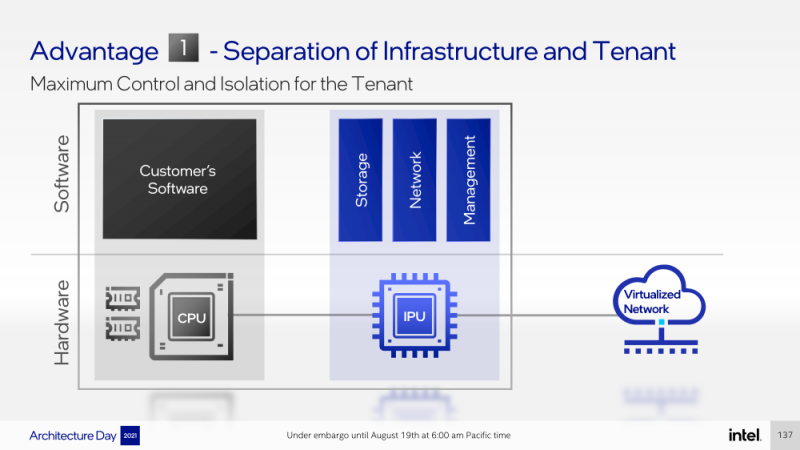

Intel объявила о совместной работе с Google над IPU Mount Evans и анонсировала IPDKIntel в рамках мероприятия Innovation раскрыла имя партнёра по разработке IPU Mount Evans — им оказалась компания Google. Впрочем, это не означает, что новинки будут доступны только ей и окажутся оптимизированы только под её задачи. IPU хоть и ориентированы в первую очередь на гиперскейлеров (среди возможных заказчиков называют и Facebook✴), но, по мнению Intel, будут интересны и менее крупным игрокам. Более того, было, наконец, прямо сказано, что ведётся работа и над Project Monterey от VMware. Как пояснил Гвидо Аппенцеллер (Guido Appenzeller), технический директор подразделения Data Platforms Group Intel, название IPU (Infrastructure Processing Unit) было выбрано в противовес всё ещё относительно новому, но более привычному термину DPU (Data Processing Unit) именно потому, что IPU охватывает более широкий спектр задач по работе именно с инфраструктурой, а не только c данными. Справедливости ради отметим, что и сами DPU, поначалу чаще ориентированные именно на ускорение работы с СХД и устранению узких мест в передаче данных, уже расширили свою функциональность и практически являются IPU именно в терминологии Intel — этот класс сопроцессоров независим от хост-системы и занимается обслуживанием инфраструктуры, включая работу с сетью и хранилищем, изоляцию и телеметрию, управление нагрузками и т.д. У Intel достаточно богатый опыт работы по сетевому направлению с гиперскейлерами. По словам Аппенцеллера, семь из восьми крупнейших компаний этого класса используют решения Intel во всей или хотя бы в некоторых частях своей инфраструктуры. Так, Microsoft, Baidu и JD полагаются на SmartNIC на базе FPGA. Партнёрство же с Google будет выгодно для обеих компаний. Intel получит заказы, а Google, наконец, обретёт то, что давно есть у Amazon — аналог Nitro. На масштабе в миллионы серверов это очень важно. Однако IPU (как аппаратные устройства) — только часть общей картины. Для полноты не хватает как минимум ещё двух компонентов: программного стека и сопутствующей инфраструктуру. Tofino-3 — анонсированный ранее чип или, как его называет сама Intel, Intelligent Fabric Processor — не только поддерживает коммутацию на скорости 25,6 Тбит/с с параллельным сбором телеметрии, но и является полностью P4-программируемым. А это позволяет организовать сквозные мониторинг, управление и оптимизацию трафика для конкретных задач. Или, иными словам, IPU и подходящие коммутаторы позволяют сделать всю инфраструктуру практически полностью программно определяемой, но с аппаратной разгрузкой части функций и близкой к bare metal итоговой производительностью. Правда, в качестве демо Intel опять же приводит «классические» примеры с СХД и Open vSwitch, а также сценарии глубокого мониторинга производительности и быстрого поиска проблемных мест в сети. Но этим потенциальные возможности не ограничиваются. Более того, со стороны ПО и средств разработки жёсткой привязки именно к «железу» Intel нет. Компания представила open source фреймворк IPDK (Infrastructure Programmer Development Kit) для упрощения переноса и, что важно, оптимизации наиболее тяжёлых или нетривиально реализуемых функций ПО на SmartNIC (с FPGA или иной программируемой логикой), IPU/DPU, коммутаторы или CPU. IPDK дополняет уже имеющиеся решения вроде DPDK, SPDK и т.д. возможностями работы с P4.

19.08.2021 [18:04], Алексей Степин

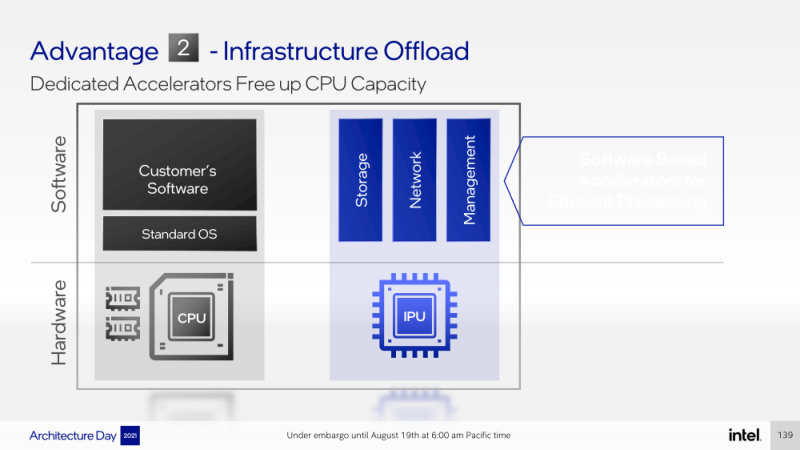

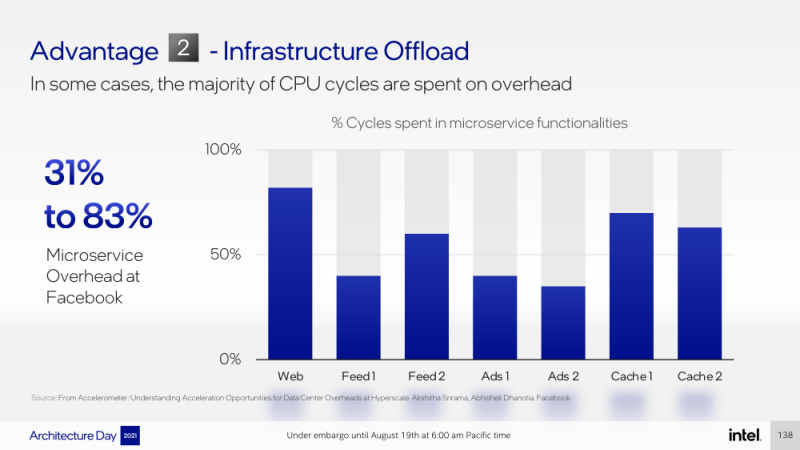

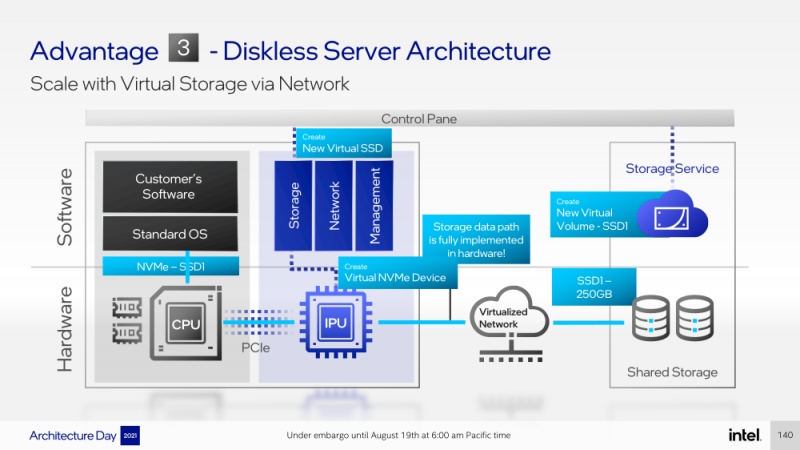

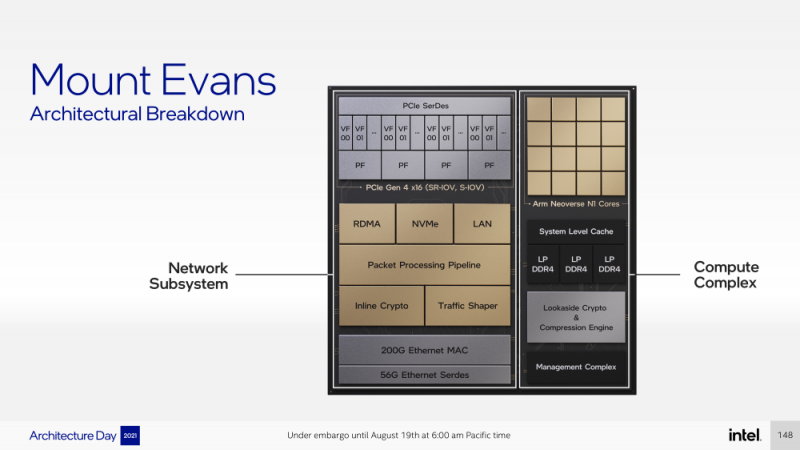

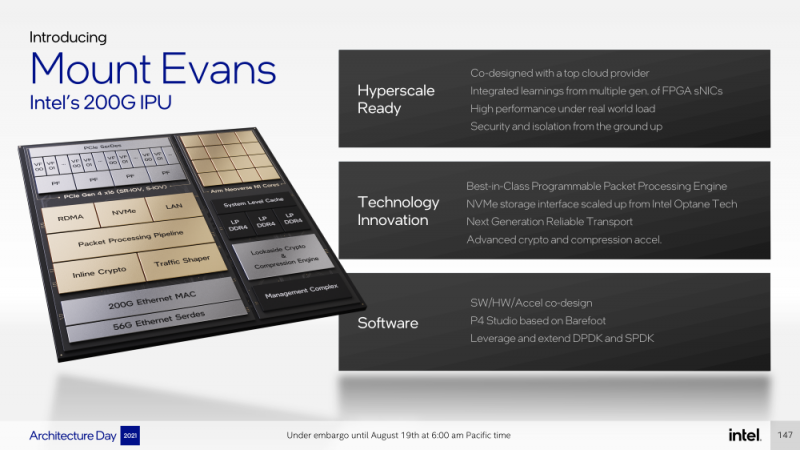

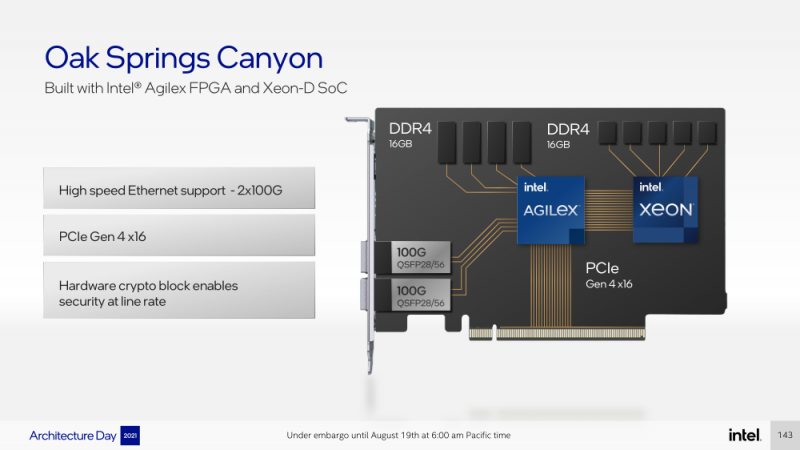

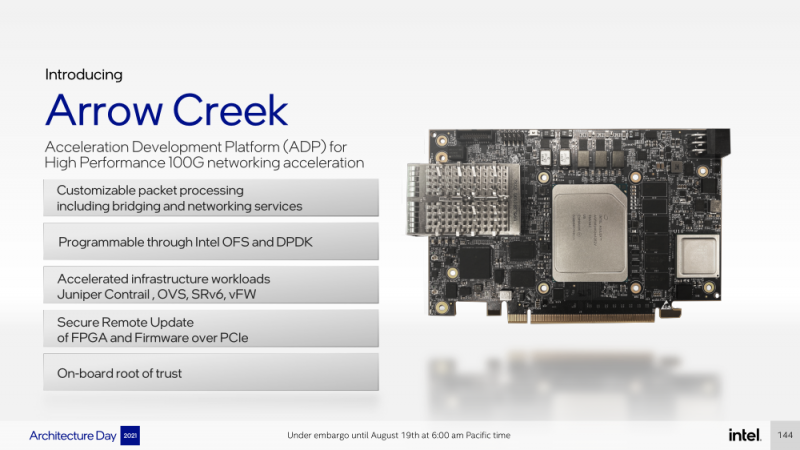

Intel представила IPU Mount Evans и Oak Springs Canyon, а также ODM-платформу N6000 Arrow CreekВесной Intel анонсировала свои первые DPU (Data Processing Unit), которые она предпочитает называть IPU (Infrastructure Processing Unit), утверждая, что такое именования является более корректным. Впрочем, цели у этого класса устройств, как их не называй, одинаковые — перенос части функций CPU по обслуживанию ряда подсистем на выделенные аппаратные блоки и ускорители. Классическая архитектура серверных систем такова, что при работе с сетью, хранилищем, безопасностью значительная часть нагрузки ложится на плечи центральных процессоров. Это далеко не всегда приемлемо — такая нагрузка может отъедать существенную часть ресурсов CPU, которые могли бы быть использованы более рационально, особенно в современных средах с активным использованием виртуализации, контейнеризации и микросервисов. Для решения этой проблемы и были созданы DPU, которые эволюционировали из SmartNIC, бравших на себя «тяжёлые» задачи по обработке трафика и данных. DPU имеют на борту солидный пул вычислительных возможностей, что позволяет на некоторых из них запускать даже гипервизор. Однако Intel IPU имеют свои особенности, отличающие их и от SmartNIC, и от виденных ранее DPU. Новый класс сопроцессоров Intel должен взять на себя все заботы по обслуживанию инфраструктуры во всех её проявлениях, будь то работа с сетью, с подсистемами хранения данных или удалённое управление. При этом и DPU, и IPU в отличие от SmartNIC полностью независим от хост-системы. Полное разделение инфраструктуры и гостевых задач обеспечивает дополнительную прослойку безопасности, поскольку аппаратный Root of Trust включён в IPU. Это не единственное преимущество нового подхода. Компания приводит статистику Facebook✴, из которой видно, что иногда более 50% процессорных тактов серверы тратят на «обслуживание самих себя». Все эти такты могут быть пущены в дело, если за это обслуживание возьмётся IPU. Кроме того, новый класс сетевых ускорителей открывает дорогу к бездисковой серверной инфраструктуре: виртуальные диски создаются и обслуживаются также чипом IPU. Первый чип в новом семействе IPU, получивший имя Mount Evans, создавался в сотрудничестве с крупными облачными провайдерами. Поэтому в нём широко используется кремний специального назначения (ASIC), обеспечивающий, однако, и нужную степень гибкости, За основу взяты ядра общего назначения Arm Neoverse N1 (до 16 шт.), дополненные тремя банками памяти LPDRR4 и различными ускорителями. Сетевая часть представлена 200GbE-интерфейсом с выделенным P4-программируемым движком для обработки сетевых пакетов и управления QoS. Дополняет его выделенный IPSec-движок, способный на лету шифровать весь трафик без потери скорости. Естественно, есть поддержка RDMA (RoCEv2) и разгрузки NVMe-oF, причём отличительной чертой является возможность создавать для хоста виртуальные NVMe-накопители — всё благодаря контроллеру, который был позаимствован у Optane SSD. Дополняют этот комплекс ускорители (де-)компресии и шифрования данных на лету. Они базируются на технологиях Intel QAT и, в частности, предложат поддержку современного алгоритма сжатия Zstandard. Наконец, у IPU будет выделенный блок для независимого внешнего управления. Работать с устройством можно будет посредством привычных SPDK и DPDK. Один IPU Mount Evans может обслуживать до четырёх процессоров. В целом, новинку можно назвать интересной и более доступной альтернативной AWS Nitro. Также Intel представила платформу Oak Springs Canyon с двумя 100GbE-интерфейсами, которая сочетает процессоры Xeon-D и FPGA семейства Agilex. Каждому чипу которых полагается по 16 Гбайт собственной памяти DDR4. Платформа может использоваться для ускорения Open vSwitch и NVMe-oF с поддержкой RDMA/RocE, имеет аппаратные криптодвижки т.д. Наличие FPGA позволяет выполнять специфичные для конкретного заказчика задачи, но вместе с тем совместимость с x86 существенно упрощает разработку ПО для этой платформы. В дополнение к SPDK и DPDK доступны и инструменты OFS. Наконец, компания показала и референсную плаформу для разработчиков Intel N6000 Acceleration Development Platform (Arrow Creek). Она несколько отличается от других IPU и относится скорее к SmartNIC, посколько сочетает FPGA Agilex, CPLD Max10 и сетевые контроллеры Intel Ethernet 800 (2 × 100GbE). Дополняет их аппаратный Root of Trust, а также PTP-блок. Работать с устройством можно также с помощью DPDK и OFS, да и функциональность во многом совпадает с Oak Springs Canyon. Но это всё же платформа для разработки конечных решений ODM-партнёрами Intel, которые могут с её помощью имплементировать какие-то специфические протоколы или функции с ускорением на FPGA, например, SRv6 или Juniper Contrail. IPU могут стать частью высокоинтегрированной ЦОД-платформы Intel, и на этом поле она будет соревноваться в первую очередь с NVIDIA, которая активно продвигает DPU BluefIeld, а вскоре обзаведётся ещё и собственным процессором. Из ближайших интересных анонсов, вероятно, стоит ждать поддержку Project Monterey, о которой уже заявили NVIDIA и Pensando.

30.06.2021 [22:44], Алексей Степин

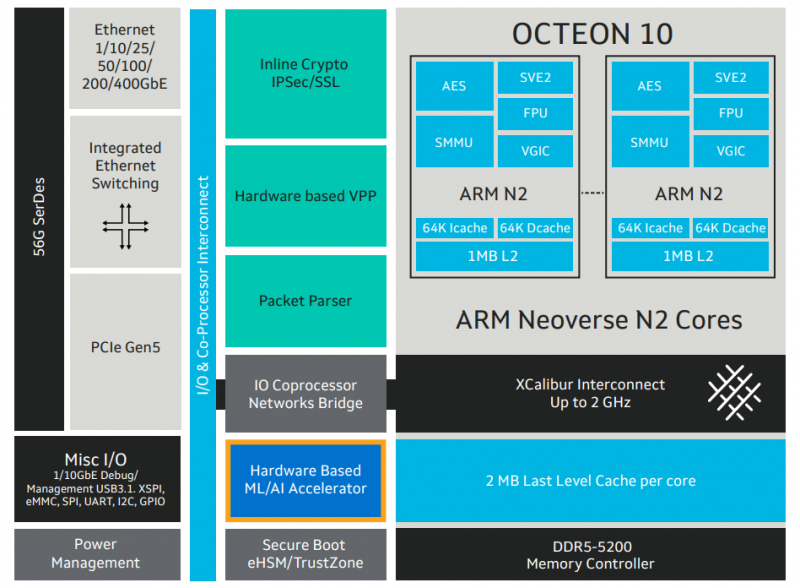

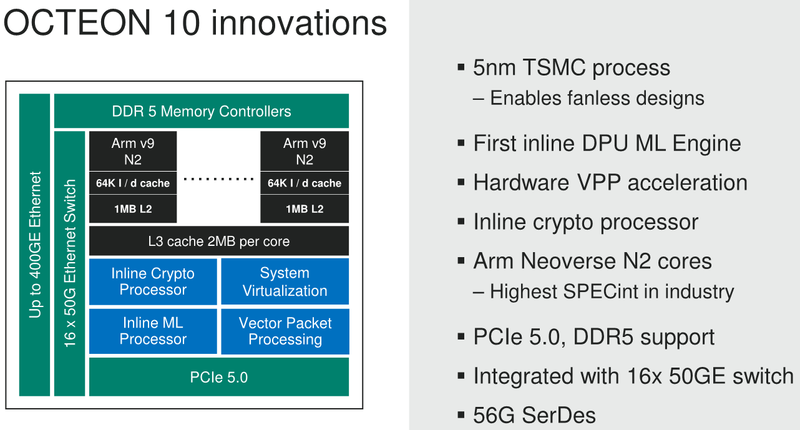

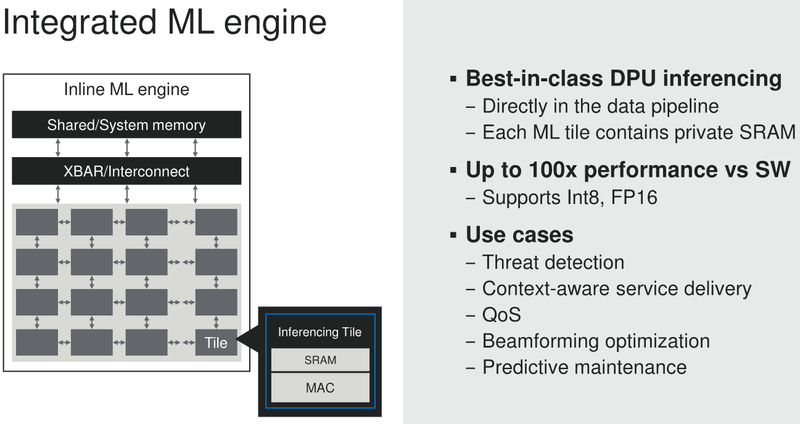

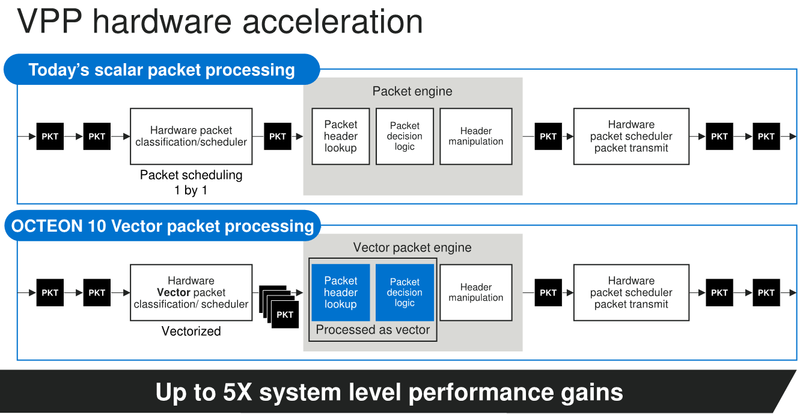

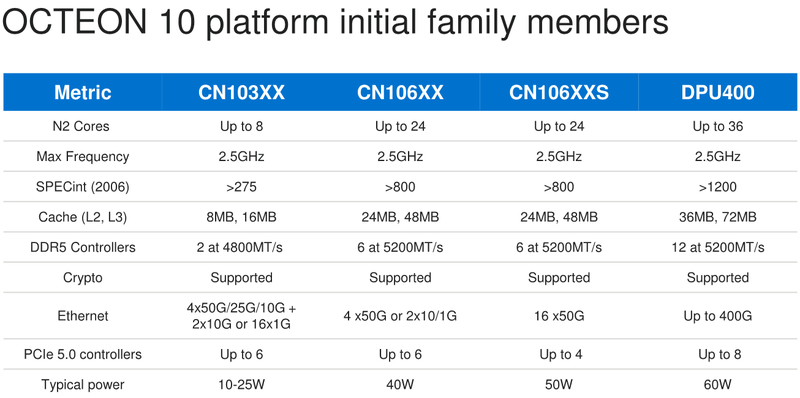

Marvell анонсировала 5-нм DPU Octeon 10: 36 ядер ARM Neoverse N2, 400GbE, PCIe 5.0 и DDR5Концепция ускорителя для работы с данными, выделенного DPU, продолжает набирать популярность. В последнее время целый ряд компаний представил свои решения. А на днях очередь дошла до крупного разработчика микроэлектроники, компании Marvell, которая анонсировала DPU серии Octeon 10. Новые сопроцессоры построены на основе наиболее совершенного 5-нм техпроцесса TSMC и должны на равных сражаться с такими соперниками, как ускорители NVIDIA BlueField. Сама Marvell известна разработкой собственных вычислительных ядер, однако в Octeon 10 от этого подхода компания отошла, вернувшись к лицензированию ядер ARM — в основу новой серии чипов легли ядра Neoverse N2.  В основе данной архитектуры лежит набор команд ARM v9, появившийся не так уж давно. В сравнении с решениями на базе ARM v8.x эта архитектура может обеспечивать до 40% прироста в производительности, в том числе, за счёт поддержки 128-битных векторных расширений SVE2 и развитой подсистемы кешей. Процессорные ядра в Octeon 10 располагают по 1 и 2 Мбайт кешей второго и третьего уровня на каждое ядро.  В составе новой SoC также присутствуют блоки ускорения сетевых задач и криптографические акселераторы. Кроме этого, кремний Octeon 10 получил и сетевой коммутатор, обеспечивающий работу 16 портов Ethernet со скоростью 50 Гбит/с. «Прокормить» столь требовательную «семью» непросто, но в плане подсистем ввода-вывода новые DPU также отвечают современным реалиям: они рассчитаны на работу с памятью DDR5-5200 и поддерживают интерфейс PCI Express 5.0, блоки SerDes относятся к поколению 56G.  Отдельного упоминания заслуживает движок векторной обработки пакетов (Vector Packet Processing Engine), способный объединять в единую серию сетевые пакеты и «переваривать» их одновременно, как векторные данные. Такой подход позволяет серьёзно снизить латентность, что для DPU очень важно. Имеются в составе Octeon 10 и средства для работы с алгоритмами машинного обучения, причём каждый «тайл», поддерживающий INT8 и FP16, имеет свой объём SRAM. Пока семейство Octeon 10 представлено четырьмя моделями, младшая из которых может содержать до 8 ядер Neoverse N2, а старшая — до 36 таких ядер, причём о масштабировании подсистемы памяти разработчики также подумали и число контроллеров DDR5 в новых чипах варьируется от 2 до 12. Несмотря на столь солидные характеристики, теплопакеты удалось удержать в разумных рамках, и даже у наиболее мощной версии DPU400 TDP составляет всего 60 Ватт.  В настоящее время Marvell Octeon 10 уже находится в производстве, первые же партии новых чипов должны поступить к заказчикам во второй половине этого года. Столь многогранные DPU должны найти применение в самых разных сценариях, от поддержания инфраструктуры 5G RAN до работы в составе облачных систем, а также в высокопроизводительных маршрутизаторах.

15.04.2021 [21:24], Игорь Осколков

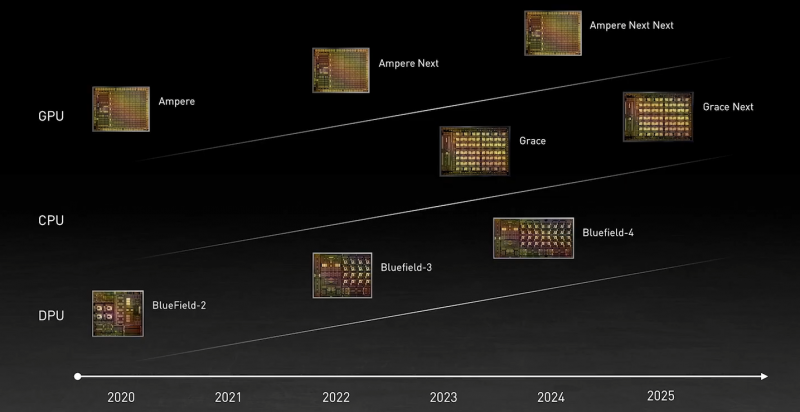

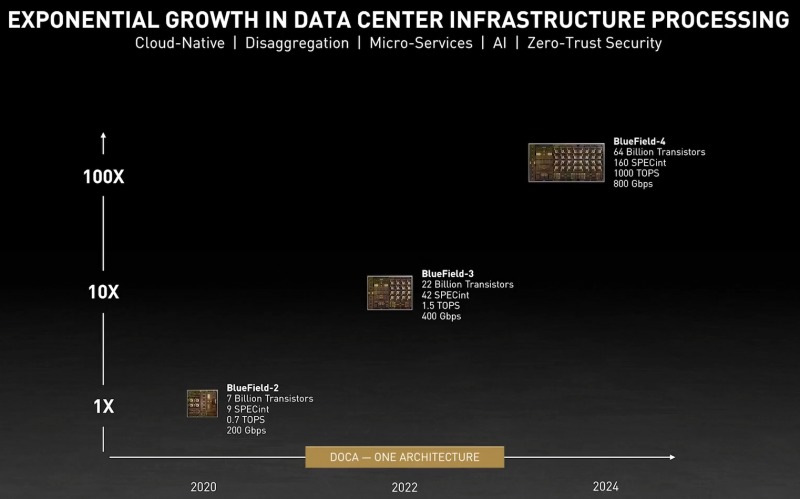

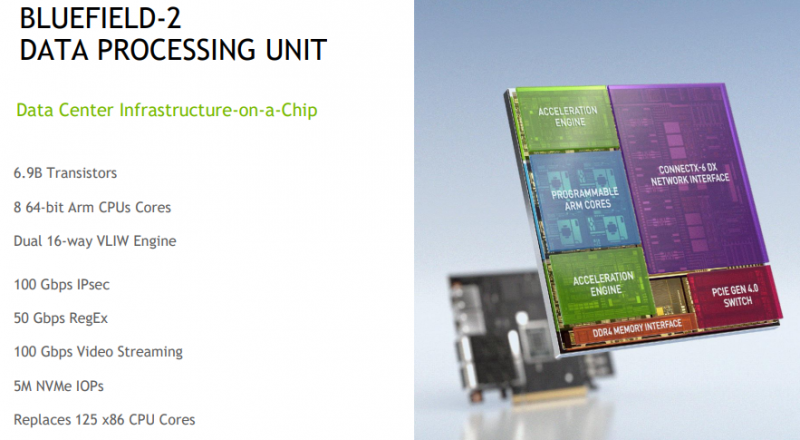

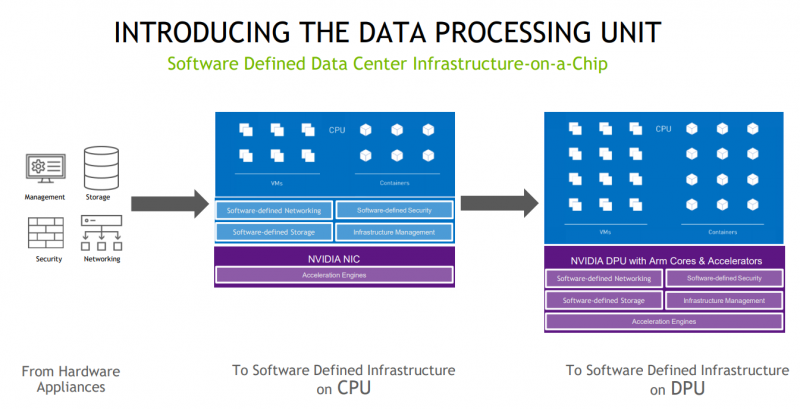

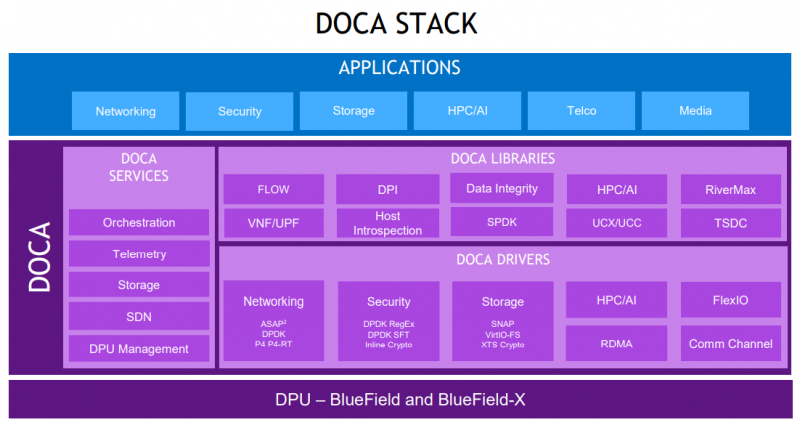

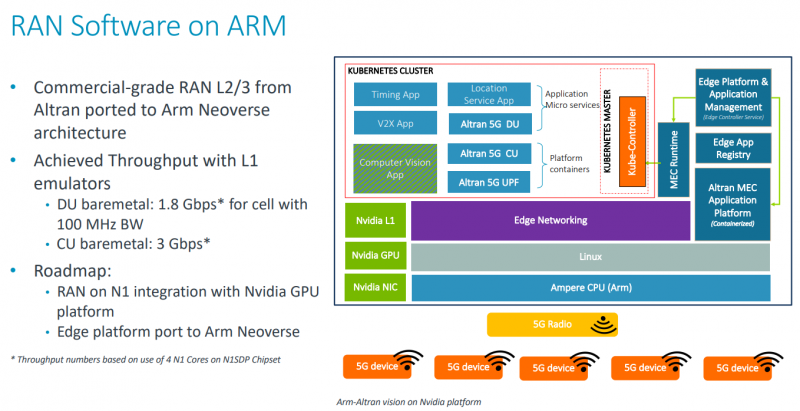

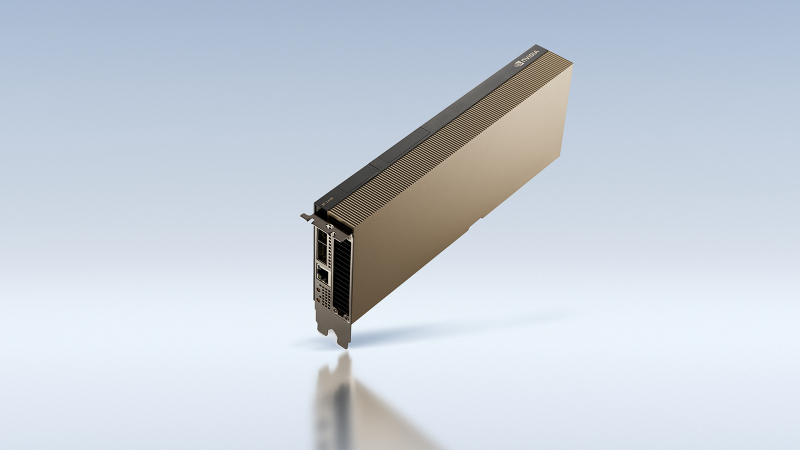

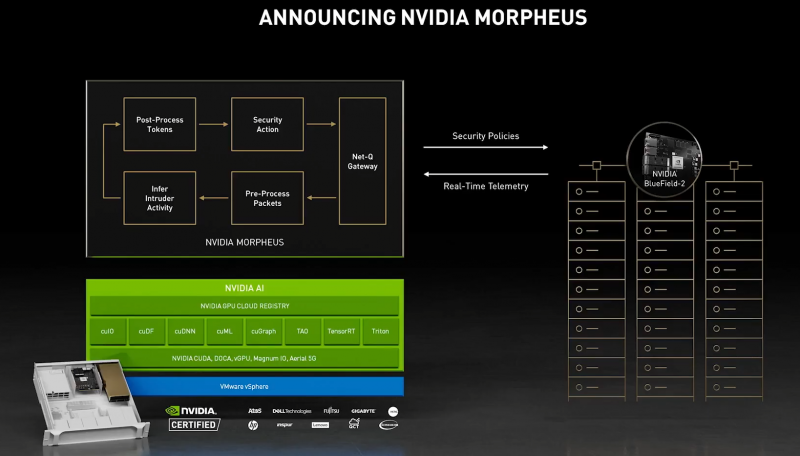

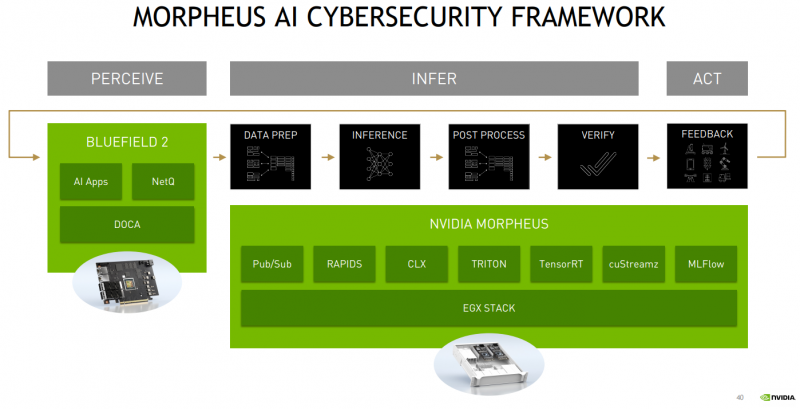

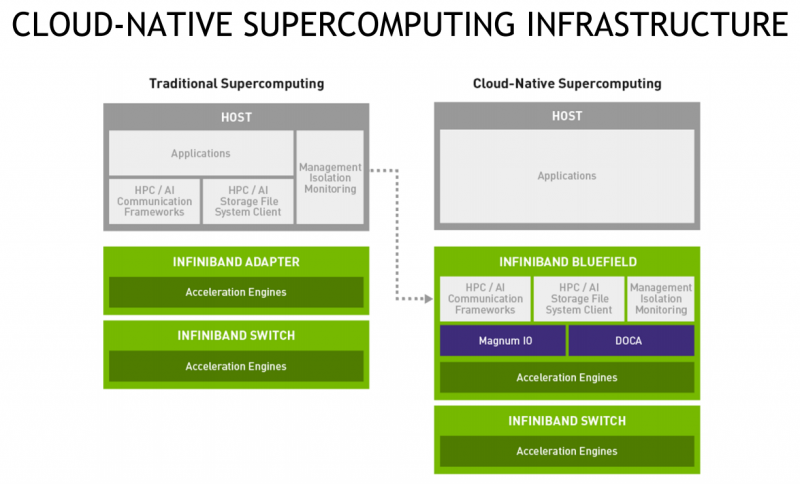

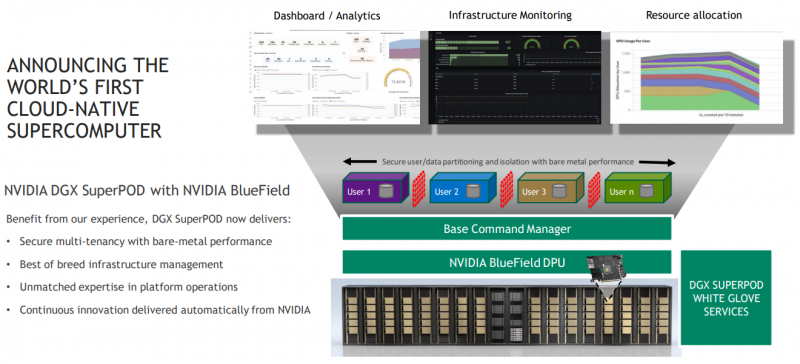

DPU BlueField — третий столп будущего NVIDIAВо время открытия GTC’21 наибольшее внимание привлёк, конечно, анонс собственного серверного Arm-процессора NVIDIA — Grace. Говорят, из-за этого даже акции Intel просели, хотя в последних решениях самой NVIDIA процессоры x86-64 были нужны уже лишь для поддержки «обвязки» вокруг непосредственно ускорителей. Да, теперь у NVIDIA есть три точки опоры, три столпа для будущего развития: GPU, DPU и CPU. Причём расположение их именно в таком порядке неслучайно. У процессора Grace, который выйдет только в 2023 году, даже по современным меркам «голая» производительность не так уж высока — в SPECrate2017_int его рейтинг будет 300. Но это и неважно потому, что он, как и сейчас, нужен лишь для поддержки ускорителей (которые для краткости будем называть GPU, хотя они всё менее соответствуют этому определению), что возьмут на себя основную вычислительную нагрузку. Гораздо интереснее то, что уже в 2024 году появятся BlueField-4, для которых заявленный уровень производительности в том же SPECrate2017_int составит 160. То есть DPU (Data Processing Unit, сопроцессор для данных) формально будет всего лишь в два раза медленнее CPU Grace, но при этом включать 64 млрд транзисторов. У нынешних ускорителей A100 их «всего» 54 млрд, и это один из самых крупных массово производимых чипов на сегодня. Значительный объём транзисторного бюджета, очевидно, пойдёт не на собственной сетевую часть, а на Arm-ядра и различные ускорители. Анонсированные в прошлом году и ставшие доступными сейчас DPU BlueField-2 намного скромнее. Но именно с их помощью NVIDIA готовит экосистему для будущих комплексных решений, где DPU действительно станут «третьим сокетом», как когда-то провозгласил стартап Fubgible, успевший анонсировать до GTC’21 и собственную СХД, и более общее решение для дата-центров. Однако подход двух компаний отличается. Напомним основные характеристики BlueField-2. Сетевая часть, представленная Mellanox ConnectX-6 Dx, предлагает до двух портов 100 Гбит/с, причём доступны варианты и с Ethernet, и с InfiniBand. Есть отдельные движки для ускорения криптографии, регулярных выражений, (де-)компрессии и т.д. Всё это дополняют 8 ядер Cortex-A78 (до 2,5 ГГц), от 8 до 32 Гбайт DDR4-3200 ECC, собственный PCIe-свитч и возможность подключения M.2/U.2-накопителя. Кроме того, будет вариант BlueField-2X c GPU на борту. Характеристики конкретных адаптеров на базе BlueField-2 отличаются, но, в целом, перед нами полноценный компьютер. А сама NVIDIA называет его DOCA (DataCenter on a Chip Architecture), дата-центром на чипе. Для работы с ним предлагается обширный набор разработчика DOCA SDK, который включает драйверы, фреймворки, библиотеки, API, службы и собственно среду исполнения. Все вместе они покрывают практически все возможные типовые серверные нагрузки и задачи, а также сервисы, которые с помощью SDK относительно легко перевести в разряд программно определяемых, к чему, собственно говоря, все давно стремятся. NVIDIA обещает, что DOCA станет для DPU тем же, чем стала CUDA для GPU, сохранив совместимость с последующими версиями ПО и «железа». На базе этого программно-аппаратного стека компания уже сейчас предлагает несколько решений. Первое — платформа NVIDIA AI Enterprise для простого, быстрого и удобного внедрения ИИ-решений. В качестве основы используется VMware vSphere, где развёртываются виртуальные машины и контейнеры, что упрощает работу с инфраструктурой, при этом производительность обещана практически такая же, как и в случае bare-metal. DPU и в текущем виде поддерживают возможность разгрузки для некоторых задач, но VMware вместе с NVIDIA переносят часть типовых задач гипервизора с CPU непосредственно на DPU. Кроме того, VMware продолжает работу над переносом своих решений с x86-64 на Arm, что вполне укладывается в планы развития Arm-экосистемы со стороны NVIDIA. Одним из направлений является 5G, причём работа ведётся по нескольким направлениям. Во-первых, сама Arm разрабатывает периферийную платформу на базе Ampere Altra, дополненных GPU и DPU. Во-вторых, у NVIDIA конвергентное решение — ускоритель Aerial A100, который объединяет в одной карте собственно A100 и DPU. При этом он может использоваться как для ускорения работы собственно радиочасти, так и для обработки самого трафика и реализации различных пограничных сервисов. Там же, где не требуется высокая плотность (как в базовой станции), NVIDIA предлагает использовать более привычную EGX-платформу с раздельными GPU (от A100 и A40 до A30/A10) и DPU. Одним из вариантов комплексного применения таких платформ является проект Morpheus. В его рамках предполагается установка DPU в каждый сервер в дата-центре. Мощностей DPU, в частности, вполне хватает для инспекции трафика, что позволяет отслеживать взаимодействие серверов, приложений, ВМ и контейнеров внутри ЦОД, а также, очевидно, применять различные политики в отношении трафика. DPU в данном случае выступают как сенсоры, данных от которых стекаются в EGX, и, вместе с тем локальными шлюзами безопасности. Ручная настройка политик и отслеживание поведения всего парка ЦОД возможны, но не слишком эффективны. Поэтому NVIDIA предлагает как возможность обучения, так и готовые модели (с дообучением по желанию), которые исполняются на GPU внутри EGX и позволяют быстро выявить аномальное поведение, уведомить о нём и отсечь подозрительные приложения или узлы от остальной сети. В эпоху микросервисов, говорит компания, более чем актуально следить за состоянием инфраструктуры внутри ЦОД, а не только на его границе, как было раньше, когда всё внутри дата-центра по умолчанию считалось доверенной средой. Кроме того, с помощью DPU и DOCA можно перевести инфраструктуру ЦОД на облачную модель и упростить оркестрацию. Но не только ЦОД — обновлённая суперкомпьютерная платформа DGX SuperPOD for Enterprise теперь тоже обзавелась DPU (с InfiniBand) и ПО Base Command, которые позволяют «нарезать» машину на изолированные инстансы с необходимой конфигурацией, упрощая таким образом совместное использование и мониторинг. А это, в свою очередь, повышает эффективность загрузки суперкомпьютера. Base Command выросла из внутренней системы управления Selene, собственным суперкомпьютером NVIDIA, на котором, например, компания обучает модели. DPU доступны как отдельные устройства, так и в составе сертифицированных платформ NVIDIA и решений партнёров компании, причём спектр таковых велик. Таким образом компания пытается выстроить комплексный подход, предлагая программно-аппаратные решения вкупе с данными (моделями). Аналогичный по своей сути подход исповедует Intel, а AMD с поглощением Xilinx, надо полагать, тоже будет смотреть в эту сторону. И «угрозу» для них представляют не только GPU, но теперь и DPU. А вот новые CPU у NVIDIA, вероятно, на какое-то время останутся только в составе собственных продуктов, в независимости от того, разрешат ли компании поглотить Arm. |

|