Материалы по тегу: чиплеты

|

03.04.2025 [16:42], Владимир Мироненко

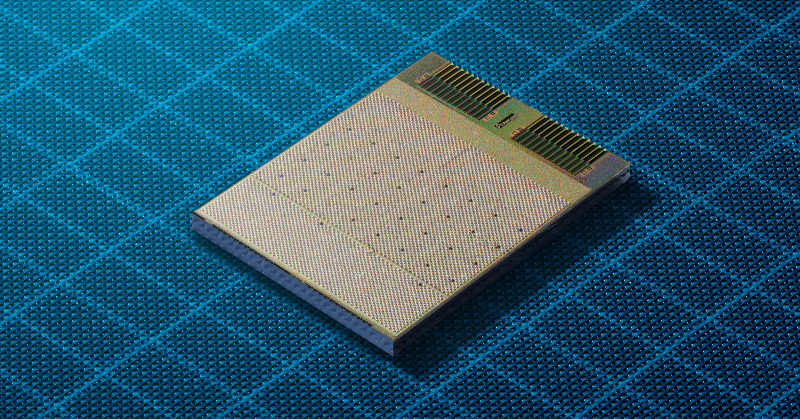

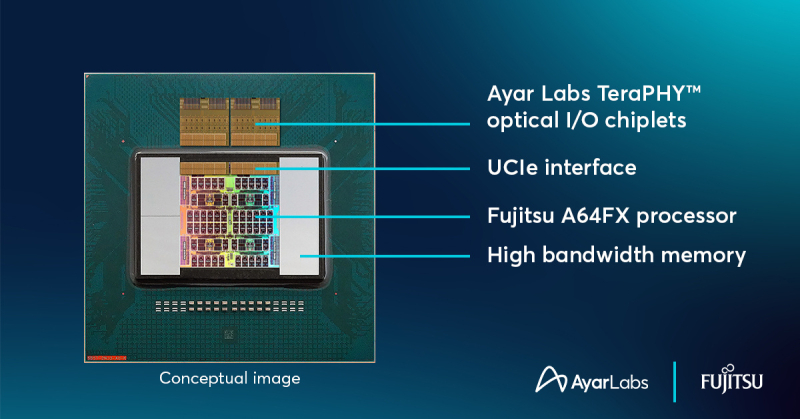

Ayar Labs анонсировала фотонный UCIe-чиплет TeraPHY с пропускной способностью 8 Тбит/сКомпания Ayar Labs, занимающаяся разработкой интерконнекта на базе кремниевой фотоники, анонсировала чиплет оптического I/O TeraPHY, способный обеспечить пропускную способность 8 Тбит/с и использующий оптический источник света SuperNova с поддержкой 16 длин волн. Чиплет поддерживает интерфейс Universal Chiplet Interconnect Express (UCIe), что означает возможность объединения в одном решении чиплетов от разных поставщиков. Ayar Labs отметила, что совместимость со стандартом UCIe позволяет создать более доступную и экономичную экосистему, которая упрощает внедрение передовых оптических технологий, необходимых для масштабирования рабочих ИИ-нагрузок и преодоления ограничений традиционных медных соединений. Ayar Labs сообщила, что объединила кремниевую фотонику с производственными процессами CMOS, чтобы обеспечить использование оптических соединений в форм-факторе чиплета в многочиповых корпусах. Это позволяет GPU и другим ускорителям взаимодействовать на широком диапазоне расстояний, от миллиметров до километров, при этом эффективно функционируя как единый гигантский ускоритель. Ранее компания совместно с Fujitsu показал концепт процессора A64FXс UCIe-чиплетом TeraPHY. Марк Уэйд (Mark Wade), генеральный директор и соучредитель Ayar Labs заявил, что в компании давно увидели потенциал совместно упакованной оптики (CPO), и поэтому занялись внедрением оптических решений в ИИ-приложениях. «Продолжая расширять границы оптических технологий, мы объединяем цепочку поставок, производство, а также процессы тестирования и проверки, необходимые клиентам для масштабного развёртывания этих решений», — подчеркнул он. Среди партнёров Ayar Labs крупнейшие компании отрасли, включая AMD, Intel, NVIDIA и TSMC. В последнем раунде финансирования, прошедшем в декабре прошлого года, компания привлекла $155 млн. Рыночная стоимость Ayar Labs, по оценкам, составляет $1 млрд.

12.03.2025 [20:37], Владимир Мироненко

Евросоюз потратит €240 млн на создание трёх RISC-V чиплетов для суперкомпьютеров в рамках проекта DARE

eurohpc

hardware

hpc

risc-v

европа

ии

импортозамещение

инвестиции

суперкомпьютер

ускоритель

финансы

чиплеты

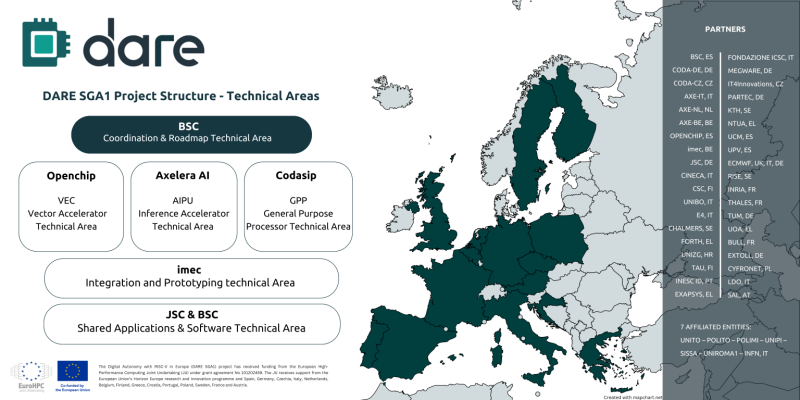

Digital Autonomy with RISC-V in Europe (DARE), крупнейший проект по разработке чипов из когда-либо финансируемых Европейским союзом, созданный с целью укрепления технологического суверенитета Европы в области высокопроизводительных вычислений (HPC) и искусственного интеллекта (ИИ), официально начал первый этап DARE SGA1, на реализацию которого выделено €240 млн ($262 млн), сообщается на сайте проекта. Европа и Китай делают ставку на RISC-V. Финансирование инициативы обеспечат 38 участников, включая ИТ-компании, исследовательские институты и университеты по всей Европе. Проект поддерживается EuroHPC JU и координируется Барселонским суперкомпьютерным центром (BSC-CNS). Последний имеет богатый опыт разработки чипов RISC-V и суперкомпьютерных систем. Половина инвестиций в проект DARE будет предоставлена Европейской комиссией через EuroHPC, а другая половина поступит напрямую от европейских партнёров, включая €34 млн от Министерства науки, инноваций и университетов Испании. Рассчитанный на три года DARE SGA1 является первым этапом шестилетней инициативы DARE. Цель — создание полноценного независимого европейского суперкомпьютерного программно-аппаратного стека для HPC и ИИ, включая чипы, системы на основе чиплетов и ПО. Инициатива направлена на удовлетворение стратегической потребности Европы в цифровом суверенитете и получения полного контроля над критической вычислительной инфраструктурой. Проектом DARE SGA1 предусмотрена разработка трёх чиплетов на основе архитектуры RISC-V, каждый из которых будет выполнять критически важную функцию в вычислениях HPC и ИИ:

В дополнение к указанным компаниям в качестве технических лидеров названы imec и Юлихский исследовательский центр (JÜLICH Supercomputing centre, JSC), которые будут продвигать ключевые инновации в рамках проекта. Помимо координации усилий, BSC также возглавит разработку планов и будет участвовать в разработке программных и аппаратных решений. Изготавливаться чиплеты будут по технологии CMOS с использованием современных техпроцессов. Axelera получит на разработку до €61 млн при условии выполнения различных задач в течение следующих трёх лет, рассказал ресурсу EE Times генеральный директор Axelera Фабрицио дель Маффео (Fabrizio del Maffeo). Хотя нынешний чип Axelera Metis AIPU предназначен для периферийных систем, дель Маффео сказал, что разрабатываемый в рамках DARE продукт на основе чиплетов не несёт кардинальные изменения, речь скорее о масштабировании. Codasip в прошлом году анонсировала 64-бит чип X730 на базе RISC-V с архитектурной защитой CHERI. По данным The Next Platform, за последнее десятилетие компания привлекла $34,6 млн общего финансирования, включая средства в рамках различных инициатив ЕС, а также посевной раунд в размере $2,5 млн в 2016 году и раунд A в размере $10 млн в 2018 году.

17.07.2024 [15:49], Руслан Авдеев

DreamBig Semiconductor получила $75 млн на развитие чиплетной платформы нового поколенияСтартап DreamBig Semiconductor получил $75 млн инвестиций. Всего, по данным Silicon Angle, за время своего существования компания привлекла $93 млн. Основанный в 2019 году стартап является создателем MARS Platform — открытой чиплетной платформы для создания решений с передовой 3D-упаковкой. Она, по словам компании, позволит создать новое поколение ИИ-чипов. Последний раунд финансирования возглавляли Samsung Catalyst Fund и Sutardja Family, участие приняли новые инвесторы в лице Hanwha, Event Horizon и Raptor. Средства дали и партнёры, уже поддержавшие проект — UMC Capital, BRV, Ignite Innovation Fund и Grandfull Fund. В компании объявили, что полученные средства потратят на ускорение развития стандарта чиплетов и коммерциализацию, а также на платформу разработки Chiplet Hub.

Источник изображения: DreamBig Ожидается, что MARS позволит клиентам сконцентрировать усилия на достижении нужных именно им характеристик чипов, а открытость платформы позволит сэкономить средства. По словам DreamBig, стандарт чиплетов MARS позволит решит проблему масштабирования вычислений и интерконнекта. Заказчики смогут использоваться базовые чиплеты для добавления той или иной функциональности к своему чипу. Заявляется, что MARS, впервые сможет обеспечить прямой доступ к SRAM и DRAM в дополнение к HBM. Для объединения кристаллов будут использоваться UCIe и BoW (Bunch of Wires), а для общения — протоколы AMBA. Платформа подходит для конструирования вычислительных чипов, ИИ-ускорителей или сетевых решений (DPU). DreamBig стала последней в серии стартапов, занятых разработкой ИИ-чипов, сумевших привлечь миллионы долларов инвестиций в этом году. Так, Etched.ai сообщил о привлечении $120 млн для того, чтобы помериться силами с NVIDIA. DEEPX привлёк $80,5 млн, SiMA Technologies получила $70 млн, а Hailo выделили $120 млн.

24.04.2024 [14:37], Сергей Карасёв

AMD: использование чиплетной архитектуры в процессорах EPYC помогает сократить выбросы парниковых газовДжастин Мюррилл (Justin Murrill), директор по корпоративной ответственности AMD, заявил, что решение компании использовать чиплетную архитектуру в процессорах EPYC позволило снизить глобальные выбросы парниковых газов на десятки тысяч тонн в год. AMD начала внедрение чиплетов около семи лет назад. Применение многокристальной архитектуры вместо монолитных изделий обеспечивает ряд преимуществ. В частности, достигается лучшая гибкость при проектировании изделий благодаря возможности комбинировать различные модули. Кроме того, повышается эффективность управления тепловыделением.

Источник изображения: AMD AMD создаёт процессоры EPYC путём компоновки вычислительных чиплетов CCD вокруг унифицированного чиплета IOD, выполняющего роль хаба ввода-вывода. Компания заявляет, что использование нескольких отдельных чиплетов вместо монолитного кристалла даёт возможность повысить процент выхода годной продукции в расчёте на одну кремниевую пластину. Дело в том, что в случае выявления дефекта отбраковывается сравнительно небольшой чип, а не крупное изделие. В результате сокращаются затраты на производство, снижаются энергетические и сырьевые потери. По словам Мюррилла, изготовление процессоров EPYC четвёртого поколения с восемью отдельными вычислительными чиплетами вместо одного монолитного кристалла позволило избежать 50 тыс. т выбросов CO2 в 2023 году. Однако нужно отметить, что это собственная оценка AMD, основанная на теоретических расчётах. Некоторые участники рынка также говорят о недостатках чиплетной компоновки. Среди минусов, в частности, называется необходимость использования высокоскоростных внутричиповых соединений. Кроме того, меньшее количество микросхем означает меньшее количество межсоединений и, следовательно, меньшую сложность и потенциально более высокую производительность.

11.04.2024 [22:27], Алексей Степин

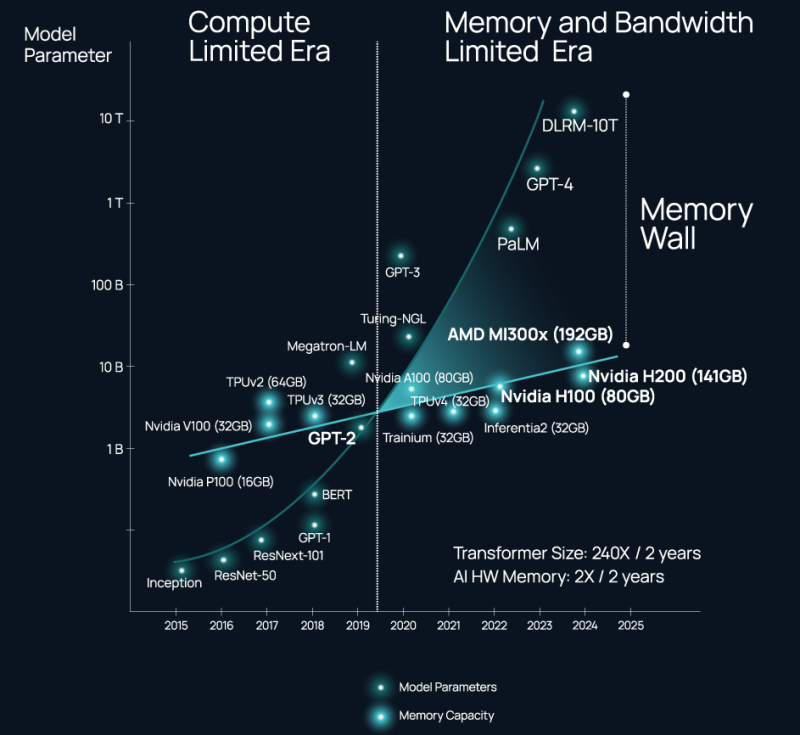

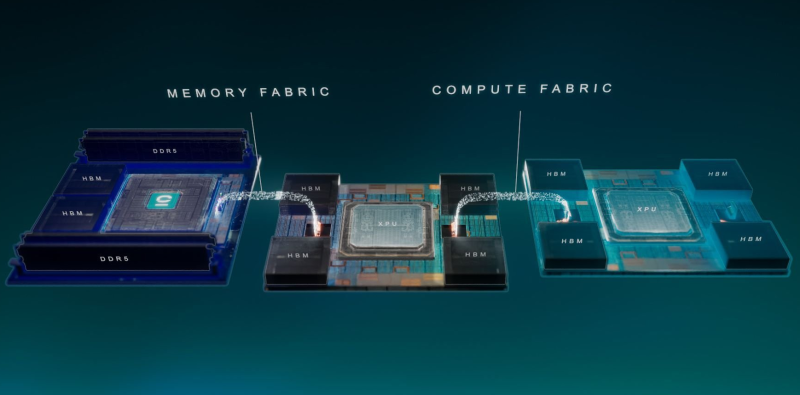

ИИ-ускорители NVIDIA являются самими дорогими в мире контроллерами памяти — Celestial AI предлагает связать оптикой HBM, DDR5 и процессорыВ 2024 году нельзя пожаловаться на отсутствие подходящего интерконнекта, если целью является «сшивка» в единую систему сотен, тысяч или даже десятков тысяч ускорителей. Есть NVIDIA NVLink и InfiniBand. Google использует оптические коммутаторы OCS, AMD вскоре выведет Infinity Fabric на межузловой уровень, да и старый добрый Ethernet отнюдь не собирается сдавать позиций и обретает новую жизнь в виде Ultra Ethernet. Проблема не в наличии и выборе подходящего интерконнекта, а в резкой потере пропускной способности за пределами упаковки чипа (т.н. Memory Wall). Да, память HBM быстра, но намертво привязана к вычислительным ресурсам, а в итоге, как отметил глава Celestial AI в комментарии изданию The Next Platform, индустрия ИИ использует ускорители NVIDIA в качестве самых дорогих в мире контроллеров памяти. Celestial AI ещё в прошлом году объявила, что ставит своей целью создание универсального «умного» интерконнекта на основе фотоники, который смог бы использоваться во всех нишах, требующих активного обмена большими потоками данных, от межкристалльной (chip-to-chip) до межузловой (node-to-node). Недавно она получила дополнительный пакет инвестиций объёмом $175 млн.

Источник изображений здесь и далее: Celestial AI Технология, названная Photonic Fabric, если верить заявлениям Celestial AI, способна в 25 раз увеличить пропускную способность и объёмы доступной памяти при на порядок меньшем энергопотреблении в сравнении с существующими системами соединений. Развивается она в трёх направлениях: чиплеты, интерпозеры и оптический аналог технологии Intel EMIB под названием OMIB. Наиболее простым способом интеграции своей технологии Celestial AI справедливо считает чиплеты. В настоящее время разработанный компанией модуль обеспечивает пропускную способность за пределами чипа на уровне 14,4 Тбит/с (1,8 Тбайт/с), а по размерам он немного уступает стандартной сборке HBM. Но это лишь первое поколение: во втором поколении Photonic Fabric 56-Гбит/с SerDes-блоки SerDes будут заменены на блоки класса 112 Гбит/с (PAM4). Поскольку речь идёт о системах с дезагрегацией ресурсов, проблему быстрого доступа к большому объёму памяти Celestial AI предлагает решить следующим образом: новый чиплет, содержащий помимо интерконнекта две сборки HBM общим объёмом 72 Гбайт, получит также поддержку четырёх DDR5 DIMM суммарным объёмом до 2 Тбайт. С использованием 5-нм техпроцесса такой чиплет сможет легко превратить HBM в быстрый сквозной кеш (write through) для DDR5. Фактически речь идёт об относительно простом и сравнительно доступном способе превратить любой процессор с чиплетной компоновкой в дезагрегированный аналог Intel Xeon Max или NVIDIA Grace Hopper. При этом латентность при удалённом обращении к памяти не превысит 120 нс, а энергозатраты в данном случае составят на порядок меньшую величину, нежели в случае с NVLink — всего 6,2 пДж/бит против 62,5 пДж/бит у NVIDIA. Таким образом, с использованием новых чиплетных контроллеров памяти становятся реальными системы, где все чипы, от CPU до сетевых процессоров и ускорителей, будут объединены единым фотонным интерконнектом и при этом будут иметь общий пул памяти DDR5 большого объёма с эффективным HBM-кешированием. По словам Celestial AI, она уже сотрудничает с некоторыми гиперскейлерами и с одним «крупным производителем процессоров». По словам руководителя Celestial AI, образцы чиплетов с поддержкой Photonic Fabric появятся во II половине 2025 года, а массовое внедрение начнется уже в 2027 году. Однако это может оказаться гонкой на выживание: Ayar Labs, другой разработчик фотоники, получившая поддержку со стороны Intel, уже показала прототип процессора с интегрированным фотонным интерконнектом. А Lightmatter ещё в декабре получила финансирование в объёме $155 млн на разработку фотонного интерпозера Passage и якобы уже сотрудничает с клиентами, заинтересованными в создании суперкомпьютера с 300 тыс. узлов. Нельзя сбрасывать со счетов и Eliyan, предлагающую вообще отказаться от технологии интерпозеров и заменить её на контроллеры физического уровня NuLink.

21.10.2023 [01:01], Алексей Степин

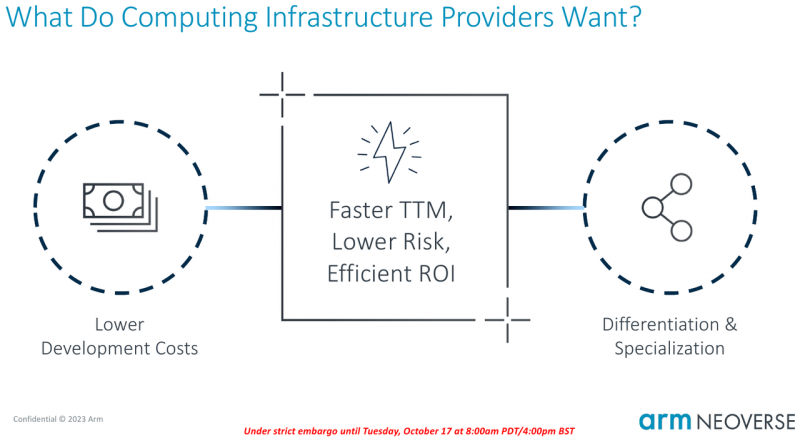

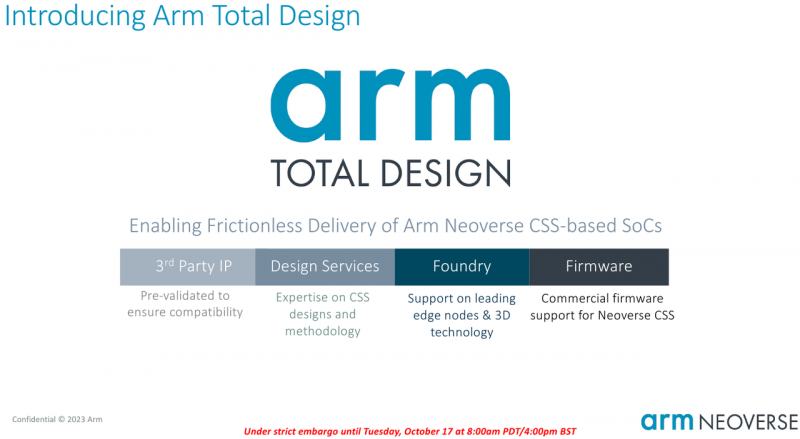

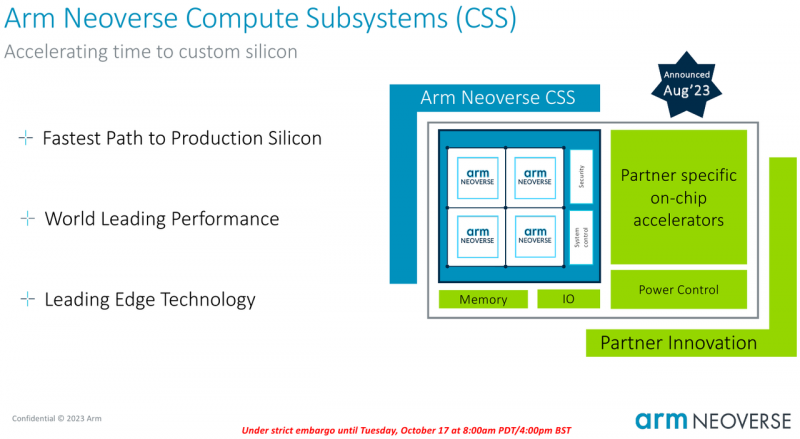

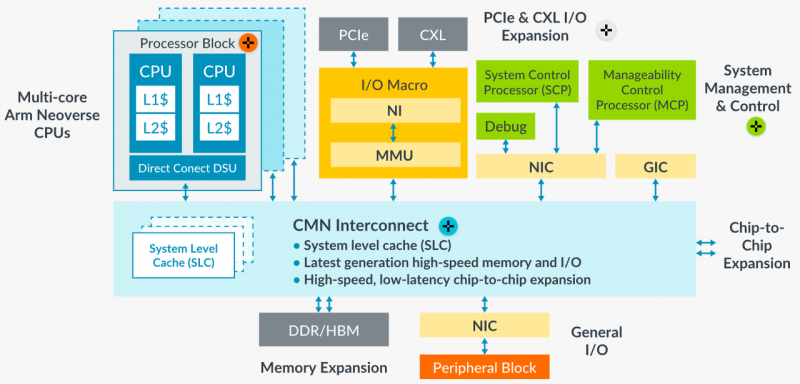

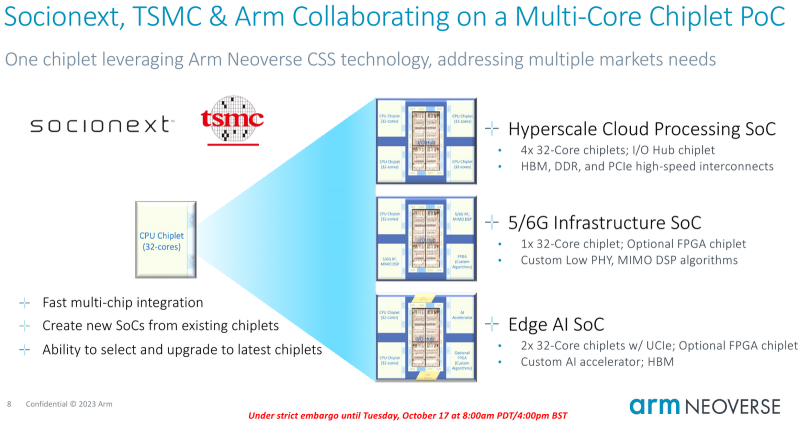

Собери сам: Arm открывает эру кастомных серверных процессоров инициативой Total DesignСегодня на наших глазах в мире процессоростроения происходит серьёзная смена парадигм: от унифицированных архитектур общего назначения и монолитных решений разработчики уходят в сторону модульности и активного использования специфических аппаратных ускорителей. Разумеется Arm не осталась в стороне — на мероприятии 2023 OCP Global Summit компания рассказала о новой инициативе Arm Total Design. Эта инициатива должна помочь как создателям новых процессоров за счёт ускорения процесса разработки и снижения его стоимости, так и владельцам крупных вычислительных инфраструктур. Последние всё больше склоняются к специализации и дифференциации в процессорных архитектурах новых поколений, но ожидают также энергоэффективности, дружественности к экологии и как можно более низкой совокупной стоимости владения. В основе инициативы Arm лежит анонсированная ещё в августе на HotChips 2023 процессорная платформа Arm Neoverse Compute Subsystem (CSS). Neoverse CSS N2 (Genesis) представляет собой готовый набор IP-решений Arm, включающий в себя процессорные ядра, внутреннюю систему интерконнекта, подсистемы памяти, ввода-вывода, управлениям питанием, но оставляющий место для интеграции партнёрских разработок — различных движков, ускорителей и т.п. По сути, речь идёт о почти готовых процессорах, не требующих длительной разработки процессорной части с нуля и всех связанных с этим процессом действий — верификации, тестирования на FPGA, валидации дизайна и многого другого. По словам Arm такой подход позволяет сэкономить разработчикам до 80 человеко-лет труда инженеров. Дизайн Neoverse CSS N2 довольно гибок: финальный процессор может включать в себя от 24 до 64 ядер Arm, работающих в частотном диапазоне 2,1–3,6 ГГц. Предусмотрено по 64 Кбайт кеша инструкций и данных, а вот объёмы кешей L2 и L3 настраиваются и могут достигать 1 и 64 Мбайт соответственно. Ядра реализуют набор инструкций Arm v9 и содержат по два 128-битных векторных блока SVE2. Имеется поддержка инструкций, характерных для ИИ-задач и криптографиии. Подсистема памяти может иметь до 8 каналов DDR5, а возможности ввода-вывода включают в себя 4 блока по 16 линий PCIe или CXL. Также возможно объединение двух чипов CSS N2 в едином корпусе, что даёт до 128 ядер на чип. В качестве внутреннего интерконнекта используется меш-сеть Neoverse CMN-700. В дизайне Neoverse CSS N2 имеются и вспомогательные ядра Cortex-M7. Они работают в составе блоков System Control Processor (SCP) и Management Control Processor (MCP), то есть управляют работой основного вычислительного массива, в том числе отвечая за его питание и тактовые частоты. Инициатива Arm Total Design расширяет рамки Neoverse Compute Subsystem: речь идёт о создании полноценной экосистемы, обеспечивающей эффективную коммуникацию между партнёрами программы Neoverse CSS и предоставление им полноценного IP-инструментария и EDA, созданных при участии Cadence, Rambus, Synopsys и др. Также подразумевается поддержка ведущих производителей «кремния» и разработчиков прошивок, в частности, AMI. В число участников проекта уже вошли такие компании, как ADTechnology, Alphawave Semi, Broadcom, Capgemini, Faraday, Socionext и Sondrel. Ожидается поддержка от Intel Foundry Services и TSMC, позволяющая говорить об эффективной реализации необходимых для мультичиповых решений технологий AMBA CHI C2C и UCIe. Будучи объединённым под одной крышей инициативы Arm Total Design, такой конгломерат ведущих разработчиков и производителей микроэлектроники и системного ПО для него, сможет в кратчайшие сроки не просто создавать новые процессоры, но и гибко отвечать на вызовы рынка ЦОД и HPC, наделяя чипы поддержкой востребованных технологий и ускорителей. В качестве примера можно привести совместный проект Arm, Socionext и TSMC, в рамках которого ведётся разработка универсального чиплетного процессора, который в различных вариантах компоновки будет востребован гиперскейлерами, поставщиками инфраструктуры 5G/6G и разработчиками периферийных ИИ-систем.

17.10.2023 [19:00], Алексей Степин

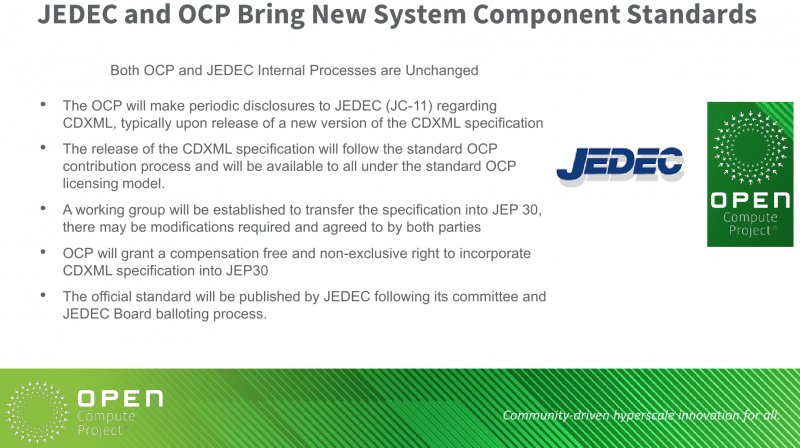

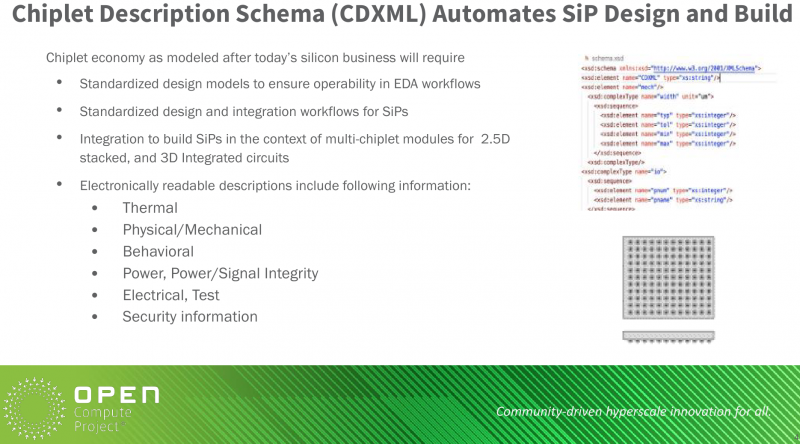

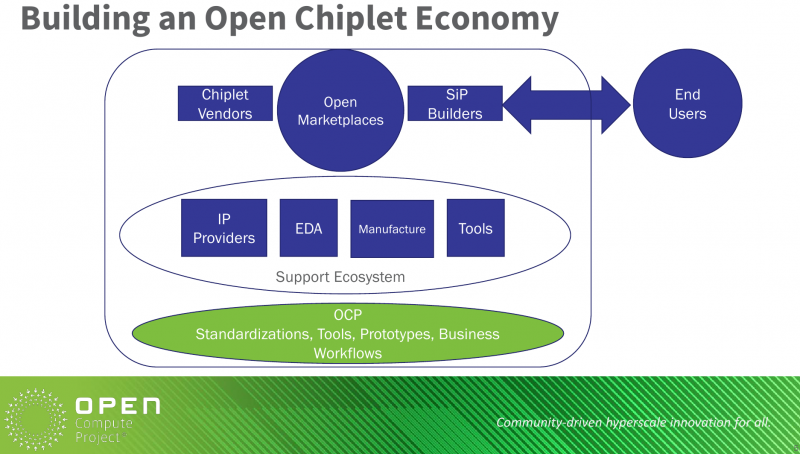

OCP и JEDEC намерены построить «чиплетную экономику»Сейчас уже очевидно, что ставка на огромные монолитные кристаллы в деле производства сложных чипов себя исчерпала и будущее за чиплетными технологиями. Но каким будет это будущее? Комитет стандартизации полупроводниковой продукции (JEDEC) и организация Open Compute Project на проходящем в настоящее время мероприятии 2023 OCP Global Summit объявили о сотрудничестве с целью выработки единого набора стандартов и унификации чиплетной экосистемы. Такой альянс способен задействовать сильнейшие стороны участников: влиятельность JEDEC в деле установления мировых стандартов в области микроэлектроники и опыт OCP в разработке устройств системного уровня, способствующий появлению новых технологий и рынков. Это позволит избежать фрагментации и излишних затрат, вызванных дублированием усилий при разработке новых устройств. OCP уже располагает спецификациями CDXML (Chiplet Data Extensible Markup Language), включающими стандартизированное описание, которое можно использовать при работе с современными средствами автоматизированного проектирования электроники (EDA). CDXML включает в себя следующие данные:

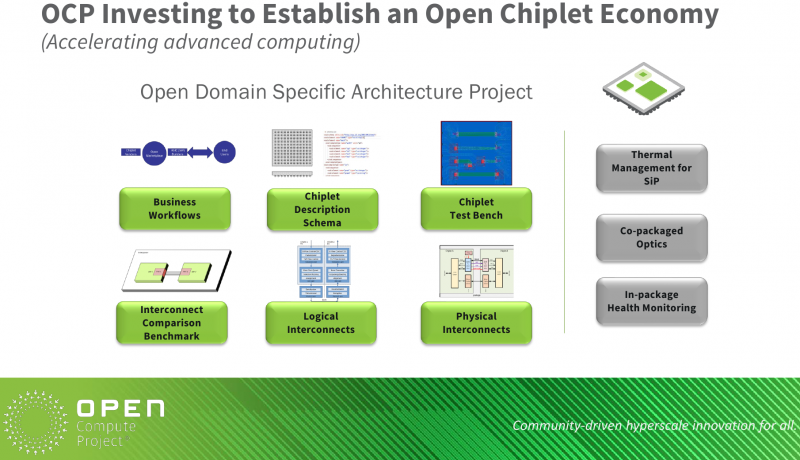

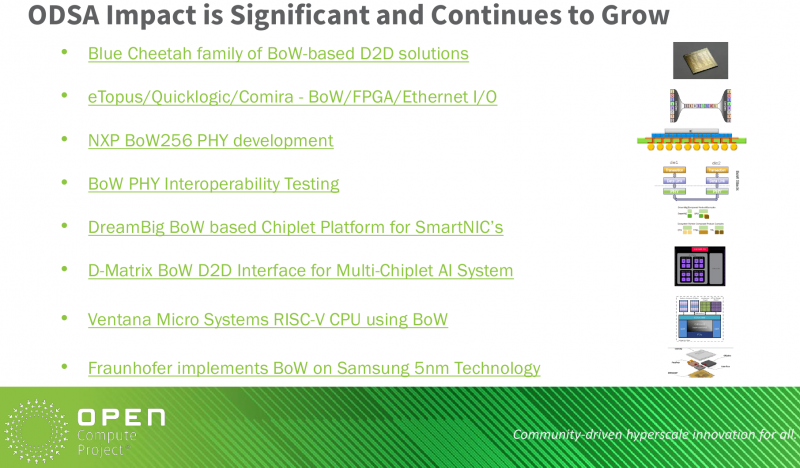

Это облегчит обмен данными между разработчиками чиплетов и их клиентами, благо уже сейчас идёт процесс интеграции CDXML в правила JEDEC JEP30 (Part Model Guidelines), описывающие процесс такого обмена. Внутренние процессы OCP и JEDEC сотрудничество не изменит, но OCP планирует регулярные поставки новых данных, относящихся к CDXML в JEDEC (JC-11) — обычно это будет связано с выпуском обновлённых версий CDXML. В соответствии с правилами лицензирования, принятыми OCP, новые данные будут доступны всем участникам консорциума. Для ускорения интеграции новых спецификаций в стандарт JEP30 будет сформирована специальная рабочая группа, в задачи которой войдёт в том числе и достижение обоюдной договорённости о внесении необходимых изменений. Официальный стандарт будет публиковаться решением комитета JEDEC в соответствии со стандартной процедурой голосования. Создание единых спецификаций CDXML открывает дорогу целому новому направлению в разработке чипов — так называемой «чиплетной экономике» (Open Chiplet Economy), в которой разработчики чиплетов смогут посредством открытого рынка взаимодействовать с производителями чипов. Такой рынок станет возможным именно благодаря созданию унифицированной экосистемы, за поддержание которой в актуальном состоянии и будет отвечать OCP. В рамках такой экономики любой проект сможет пройти от стадии описания чиплета к его тестированию с помощью специальной платформы, оценке производительности систем интерконнекта, интеграции разнородных систем, и, наконец, сборке готового решения с оценкой его термальных характеристик. Предполагается также возможность использования фотоники и наличие интегрированных средств диагностики. В рамках проекта OCP Open Domain Specific Architecture (ODSA) уже достигнуты серьёзные успехи, в число которых входит разработка высокоскоростного конфигурируемого интерконнекта Blue Cheetah класса BoW (Bunch of Wires), создание платформы DreamBig для «умных» сетевых адаптеров, использование BoW-интерконнекта в процессоре с архитектурой RISC-V и даже интеграция BoW-технологии в 5-нм техпроцесс Samsung. А сотрудничество OCP с JEDEC должно ускорить формирование «чиплетной экономики» и избежать ошибок, свойственных закрытым стандартам и платформам. |

|