Материалы по тегу: jedec

|

17.10.2023 [19:00], Алексей Степин

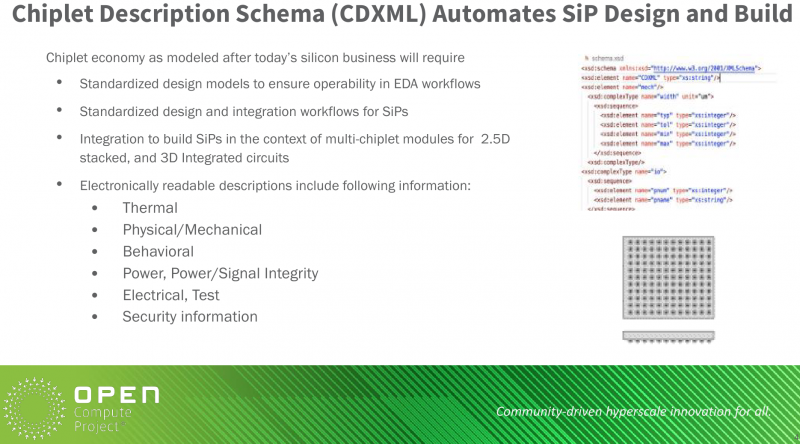

OCP и JEDEC намерены построить «чиплетную экономику»Сейчас уже очевидно, что ставка на огромные монолитные кристаллы в деле производства сложных чипов себя исчерпала и будущее за чиплетными технологиями. Но каким будет это будущее? Комитет стандартизации полупроводниковой продукции (JEDEC) и организация Open Compute Project на проходящем в настоящее время мероприятии 2023 OCP Global Summit объявили о сотрудничестве с целью выработки единого набора стандартов и унификации чиплетной экосистемы. Такой альянс способен задействовать сильнейшие стороны участников: влиятельность JEDEC в деле установления мировых стандартов в области микроэлектроники и опыт OCP в разработке устройств системного уровня, способствующий появлению новых технологий и рынков. Это позволит избежать фрагментации и излишних затрат, вызванных дублированием усилий при разработке новых устройств. OCP уже располагает спецификациями CDXML (Chiplet Data Extensible Markup Language), включающими стандартизированное описание, которое можно использовать при работе с современными средствами автоматизированного проектирования электроники (EDA). CDXML включает в себя следующие данные:

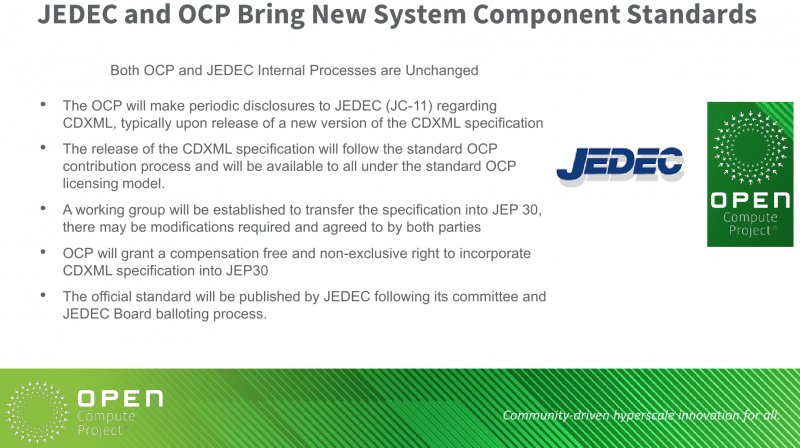

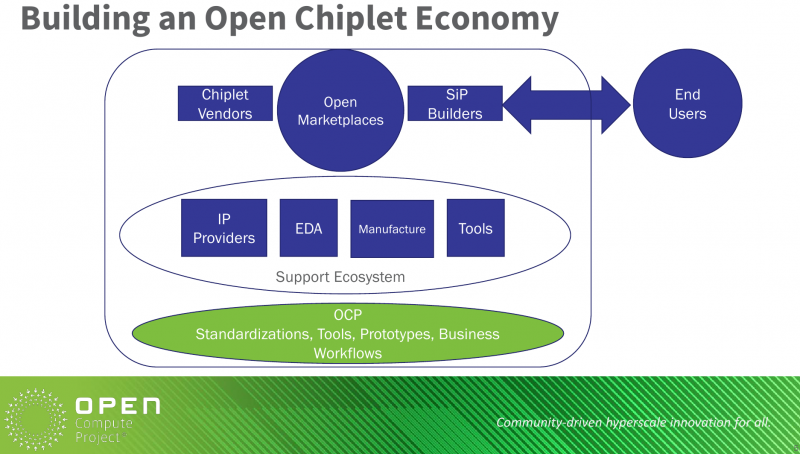

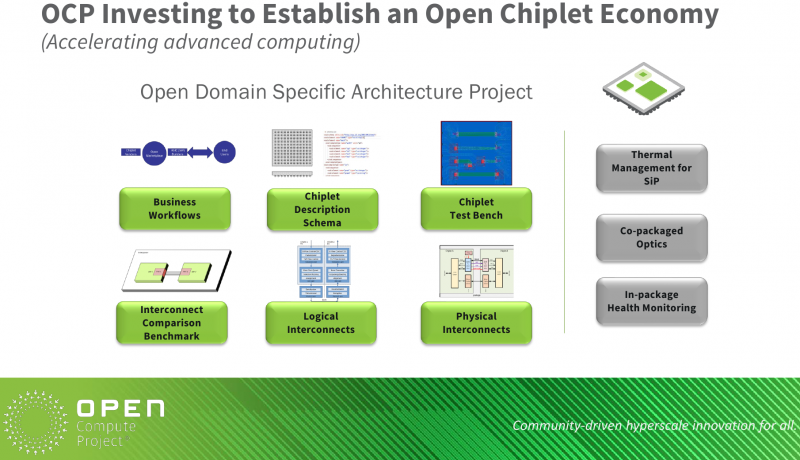

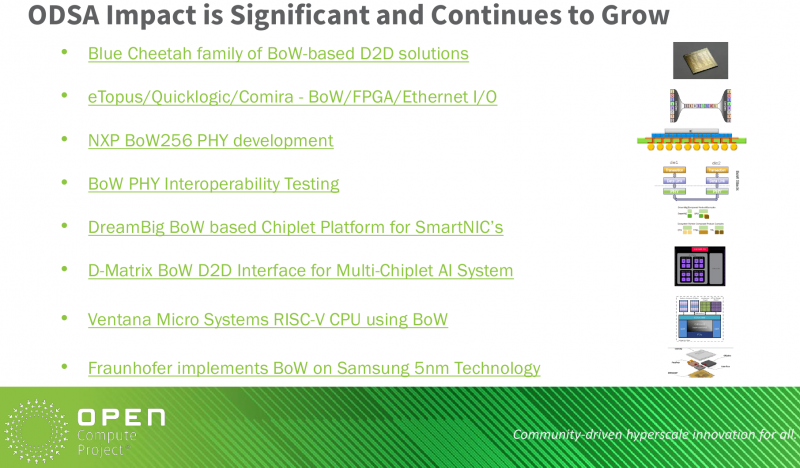

Это облегчит обмен данными между разработчиками чиплетов и их клиентами, благо уже сейчас идёт процесс интеграции CDXML в правила JEDEC JEP30 (Part Model Guidelines), описывающие процесс такого обмена. Внутренние процессы OCP и JEDEC сотрудничество не изменит, но OCP планирует регулярные поставки новых данных, относящихся к CDXML в JEDEC (JC-11) — обычно это будет связано с выпуском обновлённых версий CDXML. В соответствии с правилами лицензирования, принятыми OCP, новые данные будут доступны всем участникам консорциума. Для ускорения интеграции новых спецификаций в стандарт JEP30 будет сформирована специальная рабочая группа, в задачи которой войдёт в том числе и достижение обоюдной договорённости о внесении необходимых изменений. Официальный стандарт будет публиковаться решением комитета JEDEC в соответствии со стандартной процедурой голосования. Создание единых спецификаций CDXML открывает дорогу целому новому направлению в разработке чипов — так называемой «чиплетной экономике» (Open Chiplet Economy), в которой разработчики чиплетов смогут посредством открытого рынка взаимодействовать с производителями чипов. Такой рынок станет возможным именно благодаря созданию унифицированной экосистемы, за поддержание которой в актуальном состоянии и будет отвечать OCP. В рамках такой экономики любой проект сможет пройти от стадии описания чиплета к его тестированию с помощью специальной платформы, оценке производительности систем интерконнекта, интеграции разнородных систем, и, наконец, сборке готового решения с оценкой его термальных характеристик. Предполагается также возможность использования фотоники и наличие интегрированных средств диагностики. В рамках проекта OCP Open Domain Specific Architecture (ODSA) уже достигнуты серьёзные успехи, в число которых входит разработка высокоскоростного конфигурируемого интерконнекта Blue Cheetah класса BoW (Bunch of Wires), создание платформы DreamBig для «умных» сетевых адаптеров, использование BoW-интерконнекта в процессоре с архитектурой RISC-V и даже интеграция BoW-технологии в 5-нм техпроцесс Samsung. А сотрудничество OCP с JEDEC должно ускорить формирование «чиплетной экономики» и избежать ошибок, свойственных закрытым стандартам и платформам. |

|