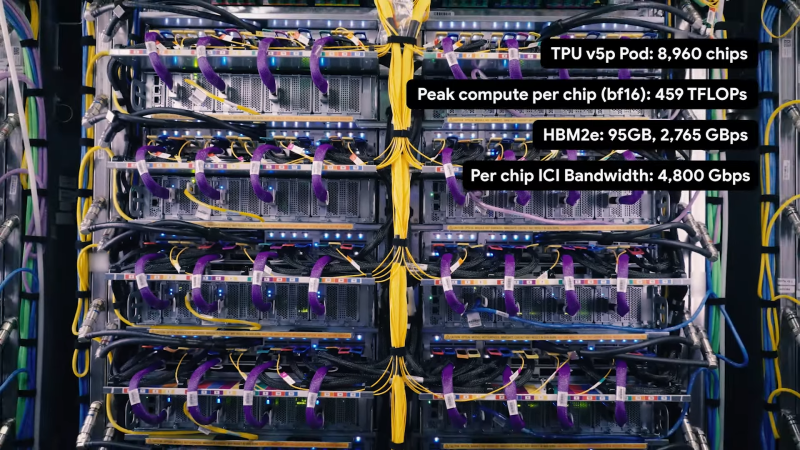

Google успешно занимается разработкой ИИ-ускорителей порядка 10 лет. В прошлом году компания заявила, что четвёртое поколение TPU в связке с фирменными оптическими коммутаторами превосходит кластеры на базе NVIDIA A100 с интерконнектом InfiniBand, а к концу того же года было представлено уже пятое поколение, причём в двух вариантах: энергоэффективные TPU v5e для малых и средних ИИ-моделей и высокопроизводительные TPU v5p для больших моделей.

Сбавлять темпа компания явно не собирается — не прошло и полугода, как было анонсировано последнее, шестое поколение TPU, получившее, наконец, собственное имя — Trillium. Клиентам Gooogle Cloud новинка станет доступна до конца этого года, в том числе в составе AI Hypercomputer. Сведений об архитектуре и особенностях Trillium пока не очень много, но согласно заявлениям разработчиков, он в 4,7 раза быстрее TPU v5e.

Источник: The Verge

Ранее аналитик Патрик Мурхед (Patrick Moorhead) опубликовал любопытное фото, на котором глава подразделения кастомных чипов Broadcom держит в руках некий XPU, разработанный для «крупной ИИ-компании». Не исключено, что сделан он именно для Google. На снимке видна чиплетная сборка из двух крупных кристаллов в окружении 12 стеков HBM-памяти. Любопытно и то, что TPU v6 нарекли точно так же, как и проект Arm шестилетней давности по созданию нового поколения ИИ-ускорителей.

Пропускная способность 32 Гбайт набортной HBM-памяти составляет 1,6 Тбайт/с. Межчиповый интерконнект ICI имеет пропускную способность до 3,2 Тбит/с, хотя в TPU v5p скорости ICI уже 4,8 Тбит/с. По словам Google, новый чип получился на 67% энергоэффективнее TPU v5e. Складывается ощущение, что компания сознательно избегает сравнения с TPU v5p. Но это объяснимо, поскольку заявленный почти пятикратный прирост производительности в сравнении с TPU v5e даёт примерно 926 Тфлопс в режиме BF16 и 1847 Топс в INT8, что практически вдвое выше показателей TPU v5p.

Кластер Google на базе TPU v5e. Источник: Google

При этом компания не бравирует высокими цифрами в INT4/FP4, как это делает NVIDIA в случае с Blackwell. Согласно опубликованным данным, прирост производительности достигнут за счёт расширения блоков перемножения матриц (MXU) и прироста тактовой частоты. В новом TPU также использовано новое, третье поколение блоков SparseCore, предназначенных для ускорения работы с ИИ-модели, часто использующихся в системах ранжирования и рекомендаций.

Масштабируется Trillium практически так же, как TPU v5e — в составе одного блока («пода») могут работать до 256 чипов. Эти «поды» формируют кластер с технологией Multislice, позволяющий задействовать в одной задаче до 4096 чипов. В таких кластерах на помощь приходят DPU Titanium, берущие на себя обслуживание IO-операций, сети, виртуализации, безопасности и доверенных вычислений. Размеры кластера могут достигать сотен «подов».

Google полагает, что TPU v6 готовы к приходу ИИ-моделей нового поколения и имеет для этого все основания: ориентировочно каждый Trillium с его 32 Гбайт быстрой памяти может оперировать примерно 30 млрд параметров, а речь, напомним, в перспективе идёт о десятках тысяч таких чипов в одном кластере. В качестве интерконнекта в таких системах используется платформа Google Jupiter с оптической коммутацией, совокупная пропускная способность которой уже сейчас превышает 6 Пбайт/с.

Источники: