Материалы по тегу: ram

|

14.08.2023 [17:37], Алексей Степин

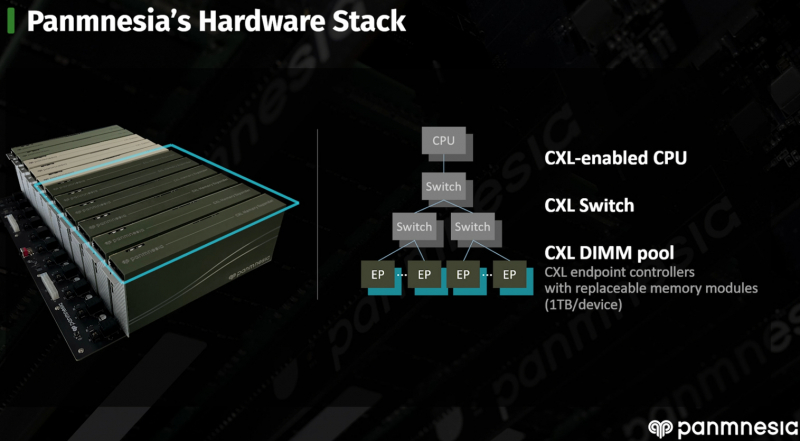

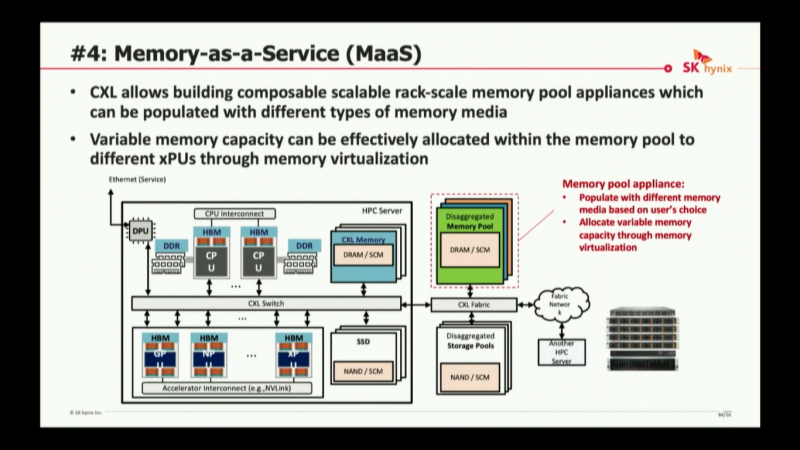

CXL-пул Panmnesia втрое быстрее RDMA-систем и может предложить 6 Тбайт RAMНа конференции Flash Memory Summit южнокорейская компания Panmnesia продемонстрировала свою версию CXL-пула DRAM объёмом 6 Тбайт на базе программно-аппаратного стека собственной разработки. Новинка продемонстрировала более чем троекратное превосходство над системой, построенной на базе технологии RDMA, в нагрузках, связанной с работой рекомендательной ИИ-системы Meta✴. Panmnesia разработана в сотрудничестве с Корейским инститом передовых технологий (KAIST). О более раннем варианте разработок KAIST в этой области мы рассказывали в 2022 году. Коммерческий вариант комплекса поддерживает CXL 3.0 и состоит из CXL-процессора, коммутатора и модулей расширения памяти. Все модули выполнены в форм-факторе, чрезвычайно напоминающем FHFL-карты. Модули устанавливаются в универсальное шасси, при этом их можно произвольно комбинировать. Демо-платформа содержала два процессорных модуля, три модуля коммутации и шесть 1-Тбайт модулей памяти. Модули памяти построены на базе обыкновенных DIMM-планок и поддерживают их замену и расширение. Реализован не только режима CXL.mem, но и CXL.cache и CXL.io. При этом компания предлагает не только готовые IP-решения, но и их кастомизацию под конкретного заказчика, что поможет оптимизировать цикл создания продукта и снизить общую стоимость разработки и валидации. Фирменное ПО базируется на Linux и содержит необходимые драйверы, а также специализированную виртуальную машину, с помощью которой пространство памяти представляется в виде безпроцессорного NUMA-узла. Поверх этих компонентов функционирует пользовательская часть, отвечающая за эффективное размещение и предвыборку (prefetching) данных. По ряду параметров Panmnesia можно назвать лидером в области CXL-решений. В частности, по объёму DRAM она уже обгоняет совместное решение Samsung, MemVerge, H3 и XConn, а использование DIMM-модулей только придаёт ей гибкости. Развитая программная часть, как утверждается, упрощает и удешевляет интеграцию в существующую инфраструктуру ЦОД. Спектр применения, как и у всех систем CXL-пулинга, крайне широкий и включает в себя не только ИИ-сценарии, но и любые задачи, требующие большого объёма оперативной памяти.

12.08.2023 [00:00], Алексей Степин

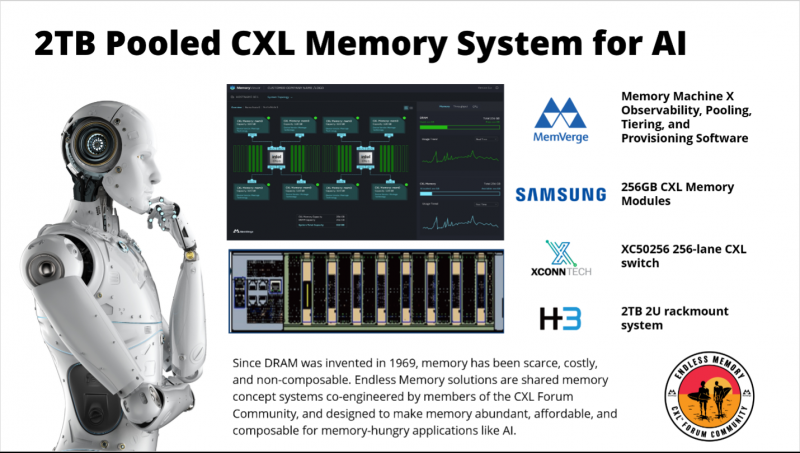

2 Тбайт RAM для ИИ: Samsung, MemVerge, H3 и XConn создали компактный CXL-пул памятиНа конференции Flash Memory Summit альянс компаний Samsung, MemVerge, H3 Platform и XConn Technologies продемонстрировал первые плоды своего сотрудничества. Речь идёт о новом CXL-пуле памяти ёмкостью 2 Тбайт, ставшим ответом на ряд проблем, с которым сталкиваются масштабные ИИ-платформы сегодня. Хостам, подключённым к пулу, можно динамически выделять требуемый объём RAM. Таких проблем, связанных со слишком тесной привязкой DRAM непосредственно к процессорам или ускорителям, можно назвать множество: потеря производительности при вынужденном сбросе данных на медленные накопители, излишнее перемещение данных из памяти и обратно, повышенная нагрузка на подсистему хранения данных, да и нехватка памяти. А памяти современным ИИ-системам требуется всё больше и больше, но наращиванию её ёмкости мешает слишком «процессороцентричная» архитектура. Многие видят здесь выход в отказе от традиционной концепции и переходе на композитную инфраструктуру, использующую возможности CXL в области организации вынесенных и легко наращиваемых при необходимости пулах памяти. Является таким пулом и демонстрируемая содружеством вышеназванных компаний система 2TB Pooled CXL Memory System.

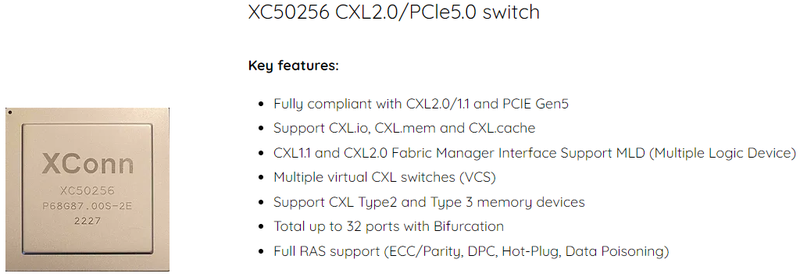

Источник изображения: Samsung Её основой стали CXL-модули Samsung ёмкостью 256 Гбайт с интерфейсом PCIe 5.0, имеющие максимальную пропускную способность до 35 Гбайт/с. В качестве связующего звена применены коммутаторы XConn Technologies XC50256 (Apollo). Эти чипы имеют 256 линий PCIe 5.0/CXL 2.0, которые группируются в 32 порта и могут обеспечить коммутацию на скорости до 2048 Гбайт/с при минимальной латентности. Как отметил представитель XConn, новые ASIC по всем параметрам превосходят аналогичные решения предыдущего поколения на базе FPGA.

Источник изображения: XConn Technologies Компания H3 Platform разработала компактное высокоплотное 2U-шасси. Также она отвечает за управляющее ПО H3 Fabric Manager, позволяющее удобно распределять CXL-ресурсы. Наконец, MemVerge ответственна за ПО, реализующее функцию «бесконечной памяти» — Memory Machine X. Этот комплекс, отвечающий за виртуализацию массивов памяти, поддерживает гибкое масштабирование, tiering, динамическое выделение памяти приложениям и многое другое, включая службу Memory Viewer, позволяющую наблюдать за топологией и загрузкой системы в реальном времени.

08.08.2023 [20:48], Алексей Степин

Micron представила CXL-модули DRAM объёмом 128 и 256 ГбайтКомпания Micron Technology анонсировала доступность первых партий CXL-модулей расширения памяти CZ120 для своих партнёров. Новые модули соответствуют стандарту CXL 2.0 Type 3 и имеют двухканальную архитектуру. Они выполнены в форм-факторе E3.S 2T (PCI Express 5.0 x8) и представлены в вариантах ёмкостью 128 и 256 Гбайт. Заявленная пропускная способность новых модулей благодаря фирменной двухканальной архитектуре составляет 36 Гбайт/с (впрочем, это может быть опечатка). В качестве сценариев применения своих новинок Micron называет ситуации, где из-за возросших нагрузок требуется всё больший объём памяти, например, для работы с ИИ или in-memory задачами — с восемью модулями CZ120 можно дополнительно получить до 2 Тбайт RAM. Также новинки должны заинтересовать гиперскейлеров.

Источник изображений здеь и далее: Micron Technology Но дело не только в объёмах — CZ120 выручит и там, где требуется дополнительная пропускная способность. В варианте с восемью модулями это означает дополнительные 256 Гбайт/с. CXL-модули несколько проигрывают в латентности традиционным DIMM, но «штраф» в этом случае не больше, нежели один переход в NUMA-системе. В настоящее время компания тесно сотрудничает с Intel в деле валидации модулей CZ120 на платформе Xeon Sapphire Rapids, которая в полном объёме поддерживает лишь CXL 1.1, но не 2.0. Также новинки показали отличный результат на платформе AMD EPYC 9754 (Bergamo) в тестах TPC-H, сообщил представитель AMD. Стоит отметить, что Micron не первой освоила DRAM-модули CXL 2.0 — ещё в мае Samsung представила свои модули объёмом 128 Гбайт в форм-факторе E3.S, всего год спустя после анонса первых в мире CXL-модулей DDR5. Свои E3.S-решения также представили SK hynix и ADATA, а Astera Labs и Montage Technology предложили экспандеры в форм-факторе плат расширения.

18.07.2023 [14:48], Сергей Карасёв

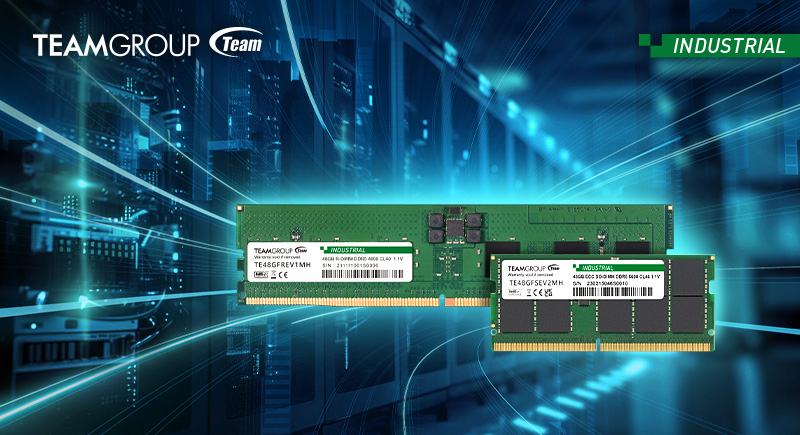

Team Group представила индустриальные модули DDR5 ёмкостью 24 и 48 ГбайтКомпания Team Group анонсировала модули оперативной памяти стандарта DDR5 для промышленного и коммерческого секторов. Это могут быть встраиваемые компьютеры, системы периферийных вычислений, высокопроизводительные рабочие станции, автомобильные компьютеры и пр. Отмечается, что обычно промышленная память DDR5 имеет ёмкость до 32 Гбайт на модуль. Однако с развитием облачных вычислений, IoT, платформ ИИ и Big Data потребность в наращивании ёмкости DDR5 возрастает.

Источник изображения: Team Group Чтобы удовлетворить спрос в корпоративном сегменте, Team Group увеличила объём промышленных изделий DDR5 до 48 Гбайт. Кроме того, заказчикам будут предлагаться решения ёмкостью 24 Гбайт. Они, как говорится, обеспечивают более высокую гибкость при развёртывании приложений разного типа и позволяют клиентам лучше справляться с обработкой больших массивов данных, сложным моделированием и аналитическими задачами. Вся промышленная память Team Group стандарта DDR5 может быть оснащена запатентованными графеновыми радиаторами, которые обеспечивают более высокую и стабильную производительность в различных температурных условиях. Новая память доступна в различных вариантах исполнения — DDR5 non-ECC U/SO-DIMM, DDR5 ECC U/SO-DIMM и DDR5 ECC R-DIMM.

14.07.2023 [19:40], Алексей Степин

Samsung и SK Hynix работают над снижением энергопотребления оперативной памятиЧем активнее внедряются ИИ-системы, тем важнее становится роль памяти HBM и DDR5, а в особенности её энергоэффективность. Так, в крупномасштабных системах на базе NVIDIA A100 на долю памяти может приходиться до 40 % потребляемой энергии. Неудивительно, что крупные производители памяти объединяют свои усилия с академическими кругами, чтобы разработать более экономичную память нового поколения. В частности, Samsung на базе CXL и 12-нм техпроцесса уже разработала чипы DDR5 ёмкостью 16 Гбайт, который на 23 % экономичнее в сравнении с аналогичными чипами предыдущего поколения. В содействии с Сеульским национальным университетом (Seoul National University) Samsung продолжает вести работы по дальнейшему снижению энергопотребления. Сам университет также ведёт исследования в этом направлении и уже разработал новую технологию DRAM Translation Layer. Ожидается, что её внедрение поможет снизить энергопотребление DRAM ещё на 31,6 %.

Источник: SK Hynix Не отстаёт от Samsung и другой крупный производитель устройств памяти, компания SK Hynix. Она представила новое поколение LPDDR5X, в котором применен техпроцесс High-K Metal Gate (HKMG). Благодаря материалу с оптимизированной диэлектрической проницаемостью удалось впятеро повысить заряд в ячейке, снизив при этом токи утечки. В итоге новая память LPDDR5X от SK Hynix может похвастаться на 33 % более высокой производительностью при 20 % экономии в энергопотреблении, в сравнении с предыдущим поколением.

08.06.2023 [15:38], Сергей Карасёв

Micron представила 96-Гбайт модули памяти DDR5-4800 RDIMMКомпания Micron Technology объявила о начале массовых поставок модулей оперативной памяти DDR5-4800 RDIMM объёмом 96 Гбайт. Изделия ориентированы на ИИ-серверы, платформы НРС, системы глубокого обучения и высоконагруженные аппаратные комплексы. По заявлениям разработчика, новые модули обеспечивают вдвое более высокую пропускную способность по сравнению с DDR4-3200 — 378 Гбайт/с против 189 Гбайт/с. Память Micron DDR5-4800 RDIMM полностью совместима с процессорами AMD EPYC Genoa. Новые модули уже применяются в сервере Supermicro 8125GS. В дальнейшем изделия возьмут на вооружение и другие поставщики серверных систем. Ранее отмечалось, что «небинарные» чипы и модули DDR5 позволят сократить расходы на память, давая возможность подобрать оптимальные количество и ёмкость DIMM и не переплачивать за избыточный объём RAM.

Источник изображения: Micron Technology «Модуль Micron DDR5 DRAM ёмкостью 96 Гбайт представляет собой новое решение, разработанное с прицелом на оптимизацию совокупной стоимости владения для наших клиентов», — заявил Правин Вайдьянатан (Praveen Vaidyanathan), вице-президент и генеральный менеджер подразделения Compute Products Group компании Micron.

03.06.2023 [14:31], Сергей Карасёв

Intel создаст лабораторию технологий для ЦОД в Южной КорееКорпорация Intel, по сообщению ресурса Businesskorea, планирует открыть в Сеуле (Южная Корея) специализированную лабораторию для тестирования компонентов для дата-центров. Ожидается, что новая исследовательская площадка начнёт функционировать до конца текущего года. Информации о размере лаборатории и планируемой численности персонала пока нет. Но известно, что Intel в рамках данной инициативы намерена взаимодействовать с южнокорейскими поставщиками серверных компонентов — прежде всего с Samsung и SK hynix. Речь идёт о тестировании передовых типов памяти, в том числе DRAM с поддержкой стандарта Compute Express Link (CXL) и DDR5. «ЦОД-лаборатория в Сеуле будет играть важную роль в проверке и сертификации памяти DRAM для использования в оборудовании с процессорами Intel. Ожидается, что Intel в рамках новой исследовательской площадки начнёт более тесно сотрудничать с Samsung Electronics и SK hynix», — заявили осведомлённые лица.

Источник изображения: Intel Отмечается также, что Intel намерена открыть в общей сложности шесть новых лабораторий. Помимо Южной Кореи, такие структуры появятся в США, Мексике, Китае, Тайване и Индии. Все они сосредоточатся на работах, связанных с полупроводниковыми и другими компонентами для серверов. Вместе с тем компания отказалась от проекта огромной лаборатории по разработке систем охлаждения для ЦОД будущего, который оценивался в $700 млн. Для Intel важно укрепление позиций на рынке ЦОД. Дело в том, что выручка корпорации в соответствующем сегменте сокращается. По итогам I четверти 2023 финансового года группа Datacenter and AI Group (DCAI) показала снижение продаж в годовом исчислении на 39 % — с $6,1 млрд до $3,7 млрд. Операционные убытки составили $518 млн против $1,4 млрд прибыли годом ранее.

03.06.2023 [14:10], Алексей Степин

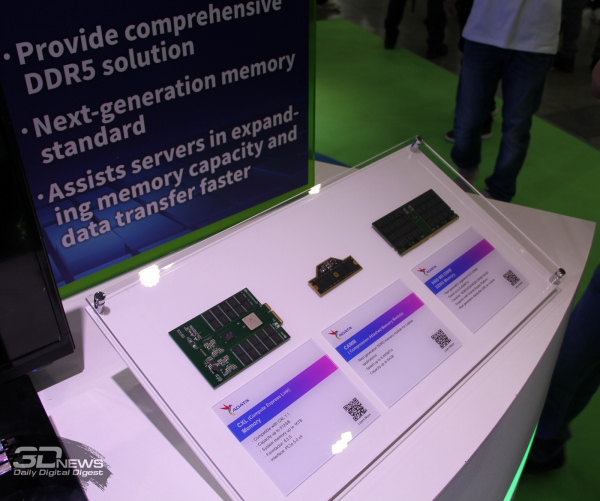

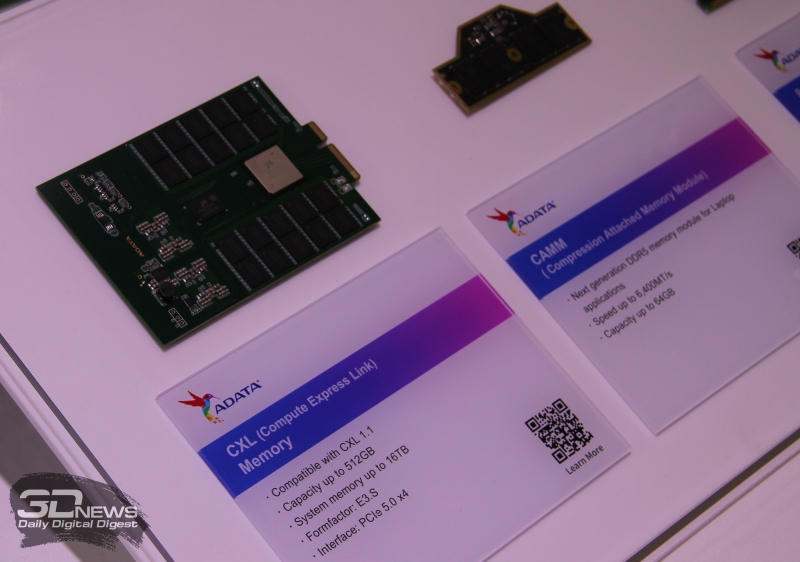

ADATA продемонстрировала память следующего поколения: CAMM, CXL и MR-DIMMНа ежегодной выставке Computex 2023 компания ADATA продемонстрировала свои первые модули памяти нового поколения, которые будут использоваться в современных вычислительных системах: CAMM, CXL и MR-DIMM. Для серверных систем компания продемонстрировала решение на базе стандарта CXL 1.1 с интерфейсом PCI Express 5.0 x4, выполненное в форм-факторе E3.S. Модуль несёт на борту контроллер Montage Technology и предназначен для расширения основного объёма оперативной памяти, подобно решениям DCPMM. При этом у Samsung, например, уже есть DRAM с поддержкой CXL 2.0. Интересно выглядит также другое серверное решение — MR-DIMM (multi-ranked buffered DIMM). Это новое поколение буферизированной памяти, поддержка которой появится в следующих поколениях процессоров AMD и Intel. По сути, такой модуль объединяет два RDIMM в одном, что позволяет поднять ёмкость и производительность «малой кровью». Скорость этих последних новинок стартует с отметки 8400 Мт/с, максимальное значение пока составляет 17600 Мт/с. Модули MR-DIMM Adata будут поставляться в объёмах 16, 32, 64, 128 и 192 Гбайт. Одним из инициаторов создания стандарта MR-DIMM (или MRDIMM) стала AMD. Intel, Renesas и SK hynix работают над похожим решением — MCR DIMM. Наконец, у компании уже есть готовый дизайн модуля CAMM в форм-факторе, который призван заменить SO-DIMM в компактных, сверхкомпактных и переносных системах. Интересно, что каждый модуль CAMM на базе LPDDR5 изначально будет поддерживать работу в двухканальном режиме. Правда, спецификации CAMM будут завершены только во второй половине этого года, так что некоторые характеристики могут измениться.

24.05.2023 [21:41], Сергей Карасёв

MemVerge представила первую в мире «бесконечную память» на базе CXLКомпания MemVerge на суперкомпьютерной конференции ISC 2023 представила, как утверждается, первую в отрасли технологию общей мультисерверной памяти на основе стандарта Compute Express Link (CXL). Проект, получивший название Gismo (Global IO-Free Shared Memory Objects), призван повысить производительность серверных платформ. Отмечается, что сетевые операции ввода-вывода и системы хранения являются узкими местами платформ распределённых приложений, интенсивно использующих данные. Решение Gismo как раз и призвано устранить данные проблемы. Речь идёт о концепции «бесконечной памяти». Применены технология CXL 2.0 (PCIe 5.0), программные компоненты службы MemVerge Elastic Memory и аппаратные решения SK hynix (Niagara Pooled Memory System). Платформа позволяет хост-серверам динамически перераспределять память по мере необходимости, чтобы избежать дефицита DRAM. Иными словами, если приложению требуется больше памяти, нежели доступно физически, сервер может использовать ПО MemVerge для получения доступа к дополнительным объёмам DRAM на других серверах посредством CXL. Утверждается, что революционная технология MemVerge призвана изменить ландшафт распределённых вычислений, давая компаниям возможность масштабировать свои операции и максимизировать производительность. Одним из первых участников проекта Gismo стала компания Timeplus — разработчик потоковой базы данных следующего поколения. Применение технологии позволило Timeplus значительно улучшить отказоустойчивость своей системы и повысить скорость обработки запросов.

12.05.2023 [13:33], Сергей Карасёв

Samsung разработала первую в отрасли память DRAM с поддержкой CXL 2.0Компания Samsung Electronics объявила о создании первой в отрасли памяти DRAM ёмкостью 128 Гбайт с поддержкой стандарта Compute Express Link (CXL) 2.0. Массовое производство изделий планируется организовать до конца текущего года. Напомним, CXL — это высокоскоростной интерконнект, обеспечивающий взаимодействие хост-процессора с акселераторами, буферами памяти, устройствами ввода/вывода и пр. Финальные спецификации CXL 2.0 были обнародованы в конце 2020 года. Память Samsung DRAM на базе CXL 2.0 использует PCle 5.0 x8 и обеспечивает пропускную способность до 35 Гбайт/с. В разработке изделия принимали участие специалисты Intel. Отмечается, что с целью создания технологий интерфейсов следующего поколения Samsung сотрудничает с рядом ЦОД, а также с производителями серверов и чипов с момента создания консорциума CXL в 2019 году.

Источник изображения: Samsung Одним из партнёров является Montage Technology: эта компания планирует организовать массовое производство контроллеров с поддержкой CXL 2.0. Стандарт CXL 2.0 позволяет формировать пулы памяти и хостам динамически выделять память по мере необходимости. Новая технология позволит клиентам повысить эффективность использования ресурсов при одновременном снижении эксплуатационных расходов. |

|