Материалы по тегу: чиплет

|

27.06.2024 [23:57], Алексей Степин

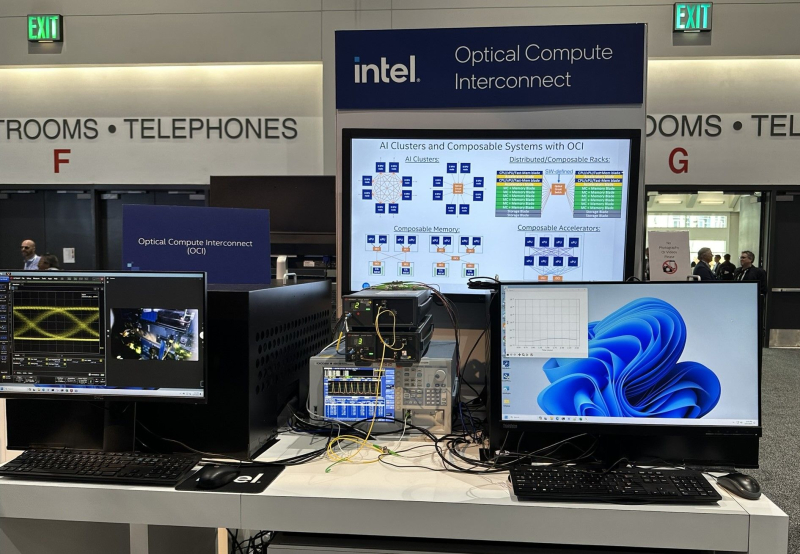

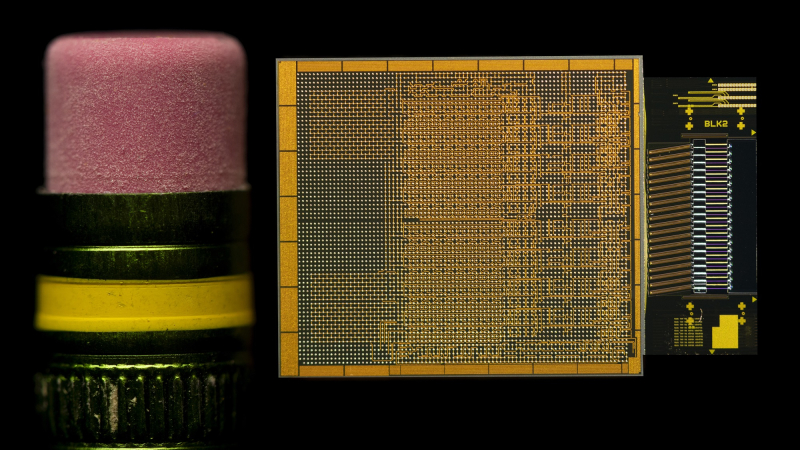

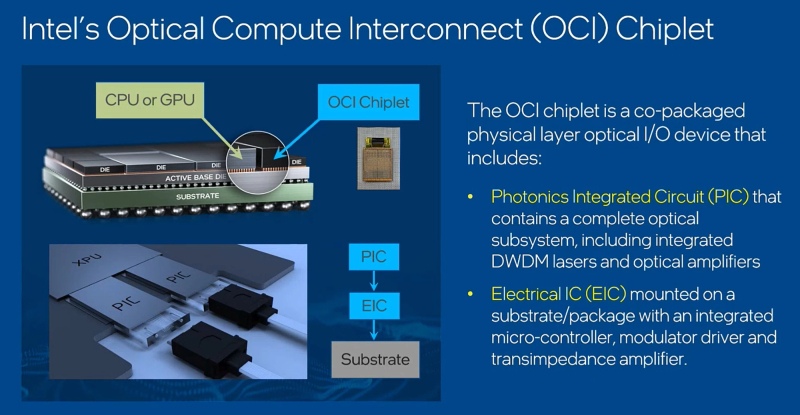

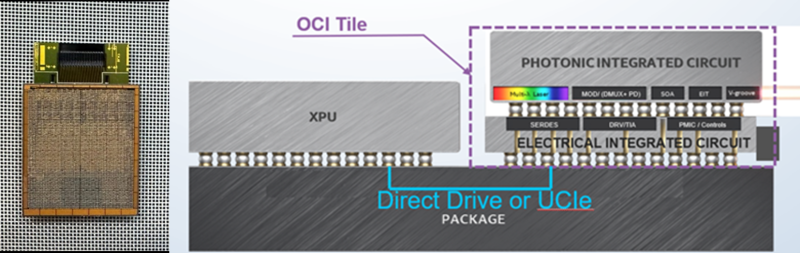

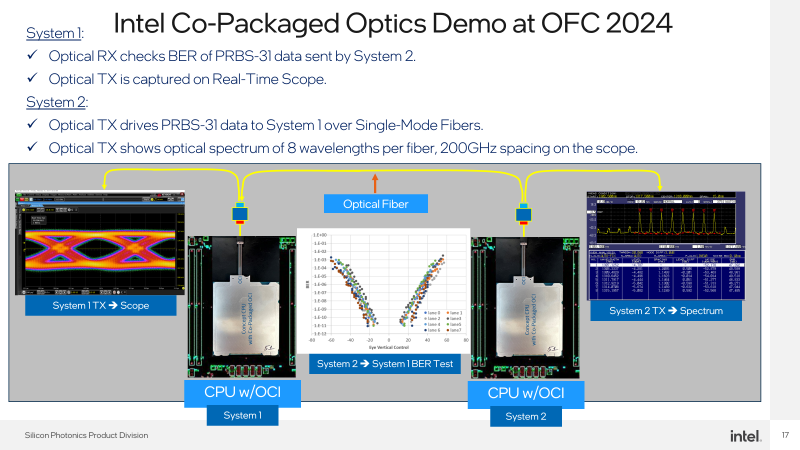

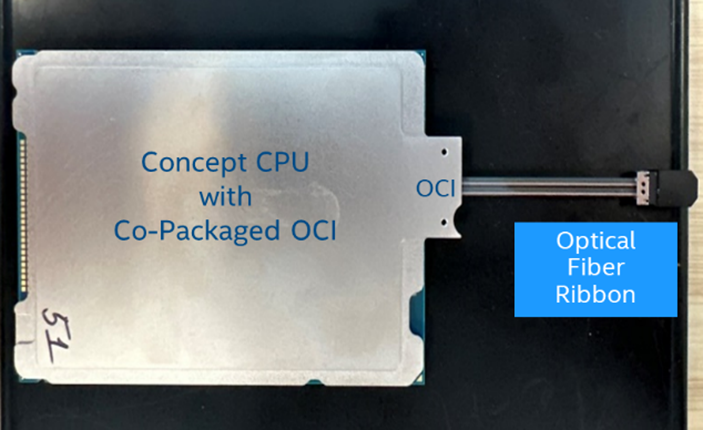

Intel представила фотонный интерконнект OCI: по 2 Тбит/с в обе стороны на расстоянии 100 мIntel ведет исследования в области интегрированной фотоники уже много лет, поскольку успех в этой сфере критически важен для HPC-систем нового поколения. Два года назад компания сообщила о создании технологии, использующей существующие техпроцессы обработки 300-мм кремниевых пластин для формирования массива лазеров вкупе с модуляторами. А сейчас можно говорить о достижении новой важной вехи в этой области. На OFC 2024 Intel продемонстрировала опытный образец CPU, оснащённый 64-канальным фотонным интерконнектом OCI (Optical Compute Interconnect). Каждый канал позволяет передавать данные на скорости 32 Гбит/с на расстоянии до 100 м, что позволит решить проблему масштабирования HPC-систем и ИИ-комплексов: пропускной способности 2 Тбит/с (256 Гбайт/с) в каждом направлении хватит на многое. А в перспективе скорость будет доведена до 32 Тбит/с. В настоящее время в системах подобного класса для высокоскоростного соединения узлов используются либо решения с внешними оптическими трансиверами, что серьёзно увеличивает стоимость и энергопотреблению в целом, либо классическую «медь», серьёзно ограниченную по максимальной длине кабеля. OCI позволяет избежать обеих проблем. Чиплет использует DWDM (восемь длин волн на волокно) и при этом экономичен: энергозатраты на передачу информации составляют всего 5 пДж/бит против 15 пДж/бит у решений с внешними оптическими трансиверами. Ранее заявленную цифру 3 пДж/бит пришлось немного увеличить, что связано с интеграцией интерфейса PCIe. Внешне продемонстрированный образец чипа напоминает выпускавшиеся когда процессоры Xeon с поддержкой Omni-Path, но вместо электрического разъёма у него теперь оптический соединитель на восемь пар волокон. С помощью простого пассивного переходника к нему в демонстрационной системе Inel был подключен типовой оптоволоконный кабель.  Поскольку речь идёт о чиплете, теоретически ничто не мешает разместить модуль OCI в составе GPU/NPU, FPGA, DPU/IPU и вообще любой модульной SoC. При этом чиплет совместим с PCIe 5.0, так что проблем с интеграцией быть не должно, хотя это и не самый оптимальный вариант. А на уровне упаковки поддерживается и UCIe. Вкупе с предельной дистанцией до 100 м новый чиплет существенно упростит системы интерконнекта: за редкими исключениями, вроде NVIDIA NVLink или Intel Gaudi 3 с его массивом Ethernet-контроллеров, связь организуется посредством PCIe-адаптера InfiniBand, либо Ethernet, в которые устанавливаются оптические трансиверы. Впрочем, и у PCI Express вскоре появится поддержка оптических подключений, что будет на руку Ultra Accelerator Link (UALink). В следующем поколении пропускная способность каждой линии OCI возрастёт с 32 до 64 Гбит/с, после чего Intel планирует довести число одновременно используемых длин волн до 16. Затем, в промежутке между 2030 и 2035 годами планируется достигнуть 128 Гбит/с на линию, уже с 16 длинами волн и 16 парами волокон. Но без конкуренции здесь не обойдётся. NVLink, который уже сейчас существенно быстрее (1,8 Тбайт/с в нынешнем поколении), вскоре тоже обзаведётся оптической версией. Похожие решения развивают Celestial AI, MediaTek и Ranovus, Lightmatter и Ayar Labs.

01.09.2021 [23:58], Андрей Галадей

Ветераны индустрии основали стартап Ventana для создания чиплетных серверных процессоров RISC-VСтартап Ventana Micro Systems, похоже, намерен перевернуть рынок серверов. Компания заявила о разработке высокопроизводительных процессоров на архитектуре RISC-V для центров обработки данных. Первые образцы фирменных CPU будут переданы клиентам во второй половине следующего года, а поставки начнутся в первой половине 2023 года. При этом процессоры получат чиплетную компоновку — различные модули и кристаллы на общей подложке. Основные процессорные ядра разработает сама Ventana, а вот остальные чиплеты будут создаваться под нужды определённых заказчиков. CPU-блоки будут иметь до 16 ядер, которые, как обещается, окажутся быстрее любых других реализаций RV64. Использование RISC-V позволит разрабатывать сверхмощные решения в рекордные сроки и без значительного бюджета. Ядра будут «выпекаться» на TSMC по 5-нм нормам, но для остальных блоков могут использовать другие техпроцессы и фабрики.  Ventana будет следить за процессом их создания и упаковывать до полудюжины блоков в одну SoC. Для соединения ядер, кеша и других компонентов будет использоваться фирменная кеш-когерентная шина, которая обеспечит задержку порядка 8 нс и скорость передачи данных 16 Гбит/с на одну линию. Основными заказчиками, как ожидается, станут гиперскейлеры и крупные IT-игроки, которым часто требуется специализированное «железо» для ЦОД, 5G и т.д. Сегодня Ventana объявила о привлечении $38 млн в рамках раунда B. Общий же объём инвестиций составил $53 млн. Компания была основана в 2018 году. Однако это не совсем обычный стартап — и сами основатели, и команда являются настоящими ветеранами индустрии. Все они имеют многолетний опыт работы в Arm, AMD, Intel, Samsung, Xilinx и целом ряде других крупных компаний в области микроэлектроники. Часть из них уже имела собственные стартапы, которые были поглощены IT-гигантами. |

|