Материалы по тегу: agilex

|

12.03.2025 [14:57], Сергей Карасёв

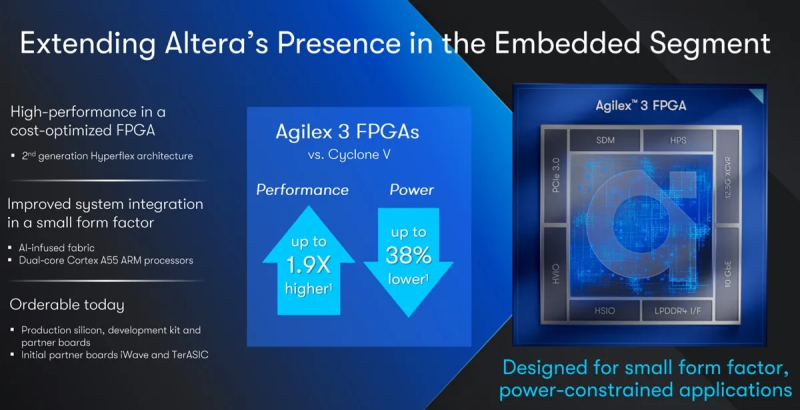

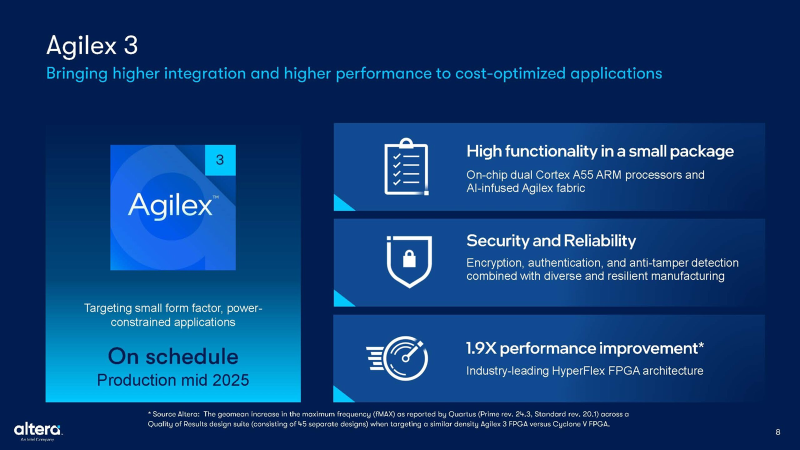

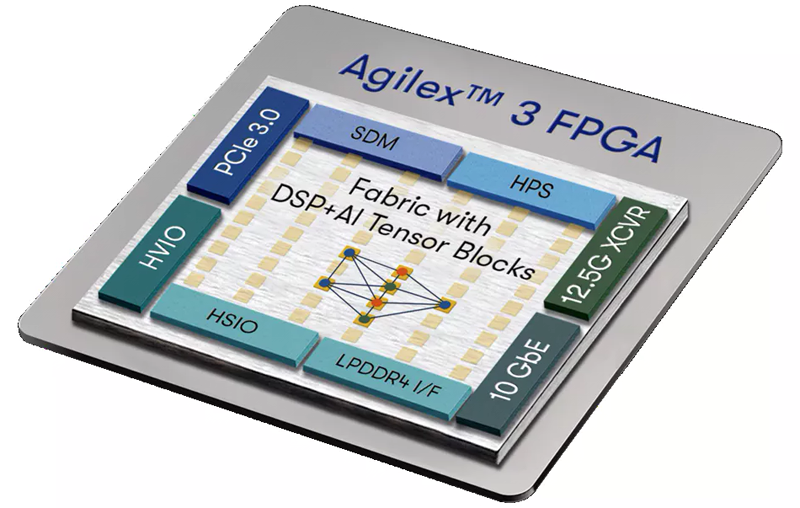

Altera представила малые FPGA семейства Agilex 3 для энергоэффективных системКомпания Altera, сформированная на базе выделенной из Intel группы программируемых решений (PSG), анонсировала FPGA семейства Agilex 3 для маломощных и экономичных систем. Среди сфер применения изделий названы автоматизация производственных процессов, медицинская визуализация, видеонаблюдение, мониторинг транспортных систем, периферийные ИИ-вычисления и пр. О подготовке Agilex 3 сообщалось в сентябре прошлого года. Задействована архитектура HyperFlex второго поколения. В состав решений входят ПЛИС с возможностями ИИ и два ядра Arm Cortex-A55 с тактовой частотой 800 МГц. По заявлениям Altera, чипы Agilex 3 обеспечивают 1,9-кратный рост производительности по сравнению Cyclone V при снижении энергопотребления до 38 %. Для трансиверов Agilex 3 заявлена скорость передачи данных до 12,5 Гбит/с. Говорится о поддержке интерфейсов PCIe 3.0 x4 и 10GbE. Усовершенствованный цифровой сигнальный процессор с блоком AI Tensor Block обеспечивает пиковую ИИ-производительность 2,8 TOPS на операциях INT8. Реализованы различные средства обеспечения безопасности, включая защищённую загрузку, шифрование AES и управление конфигурацией FPGA.  В семейство Agilex 3 вошли модели A3C025, A3C050, A3C065, A3C100 и A3C135, насчитывающие от 25 075 до 135 110 логических элементов. Поддерживается работа с памятью LPDDR4-2133. Изделия могут быть выполнены в корпусе с размерами 12 × 12, 16 × 16 или 18 × 18 мм. В качестве примеров использования Agilex 3 компания Altera приводит роботизированные системы, где FPGA обеспечивают управление в реальном времени для многоосевых манипуляторов. В составе промышленных камер чипы улучшают обнаружение дефектов. Приём предварительных заказов на изделия уже начался.

24.09.2024 [20:05], Владимир Мироненко

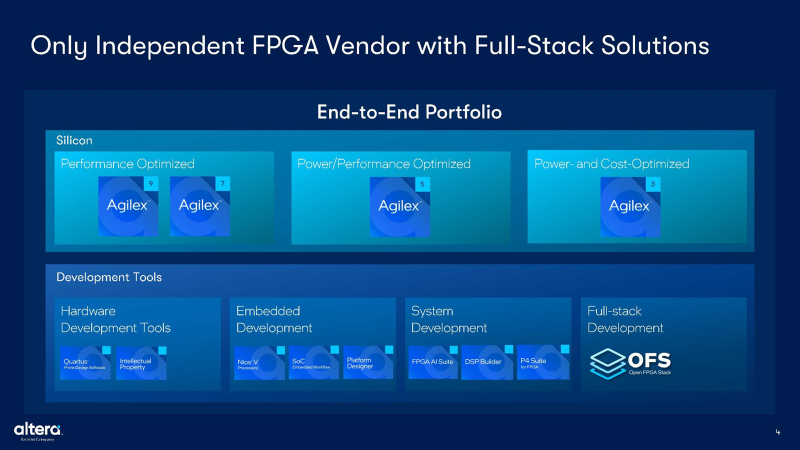

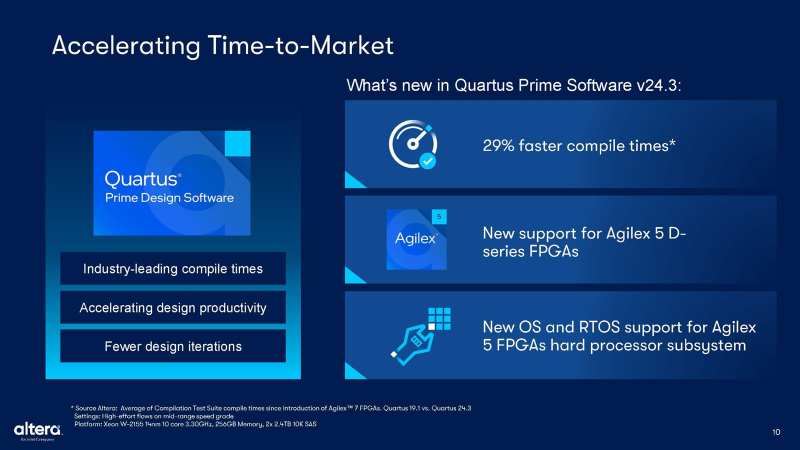

Altera поделилась подробностями об FPGA Agilex 3 и анонсировала предстоящий релиз Quartus Prime ProКомпания Altera, созданная на базе выделенной из Intel группы программируемых решений (PSG), поделилась на ежегодной конференции для разработчиков Altera Innovators Day новыми подробностями о следующем поколении оптимизированных по энергопотреблению и стоимости чипов Agilex 3, а также анонсировала новые комплекты разработки и поддержку ПО для FPGA Agilex 5. Altera сообщила, что новые FPGA Agilex отличается от предыдущего поколения более высоким уровнем интеграции, повышенной безопасностью и более высокой производительностью, объединяя эти качества в компактном корпусе с плотностью от 25 тыс. до 135 тыс. логических элементов. Наряду с ПЛИС, наделённой возможностями ИИ, семейство Agilex 3 содержит пару Arm-ядер Cortex-A55. FPGA серии Agilex 3 ориентированы на системы, в которых энергоэффективность важнее производительности. Intel полагает, что эти чипы найдут применение в таких продуктах, как подключённые устройства, промышленные роботы и автономные транспортные средства. Для интеллектуальных периферийных приложений именно FPGA обеспечивают вычисления в реальном времени для чувствительных ко времени приложений. А для интеллектуальных технологий автоматизации производства Agilex 3 предложат бесшовную интеграцию датчиков, драйверов, актуаторов и алгоритмов машинного обучения. Agilex 3 используют архитектуру HyperFlex и имеют в 1,9 раза более высокую производительность по сравнению с предыдущим поколением, говорит Altera. Рост производительности достигнут за счёт интегрированных высокоскоростных трансиверов (до 12,5 Гбит/с) и поддержки экономичной памяти LPDDR4. Для удовлетворения потребности как оборонных систем, так и коммерческих проектов в области безопасности, в Agilex 3 добавлено шифрование потоков данных, аутентификация и функция обнаружения физического несанкционированного доступа. Компания сообщила, что ПО для Agilex 3 FPGA выйдет в I квартале 2025 года, а поставки комплектов разработчика и самого продукта, как ожидается, начнутся в середине 2025 года. Altera также анонсировала предстоящий выпуск ПО Quartus Prime Pro 24.3 для современных ПЛИС Agilex и расширенную поддержку встраиваемых решений. Речь как об аппаратных блоках, так и, например, о программном RISC-V ядре Nios V. Кроме того, объявлено о поддержке Agilex 5 SoC в Linux, VxWorks и Zephyr. Клиенты смогут использовать Quartus Prime Pro 24.3 для серии Agilex 5 D, которая нацелена на более широкий спектр вариантов использования по сравнению с Agilex 5 E, оптимизированной для обеспечения эффективных вычислений на периферии. При этом для Agilex 5 E-серии доступна бесплатная лицензия ПО Quartus Prime, что снизит барьер для входа при работе с FPGA Altera среднего уровня. Также отмечена выросшая почти на треть скорость компиляции. Наконец, Altera и её партнеры по экосистеме объявили о выпуске 11 новых комплектов разработчика на основе Agilex 5 и SoM. В дальнейшем Altera сосредоточится именно на работе с партнёрами, а сама заниматься созданием плат и решений вряд ли будет.

23.05.2023 [15:01], Сергей Карасёв

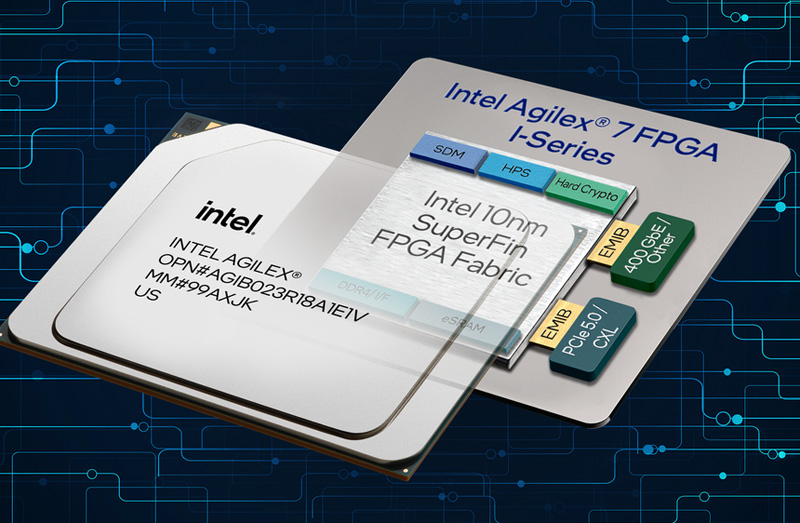

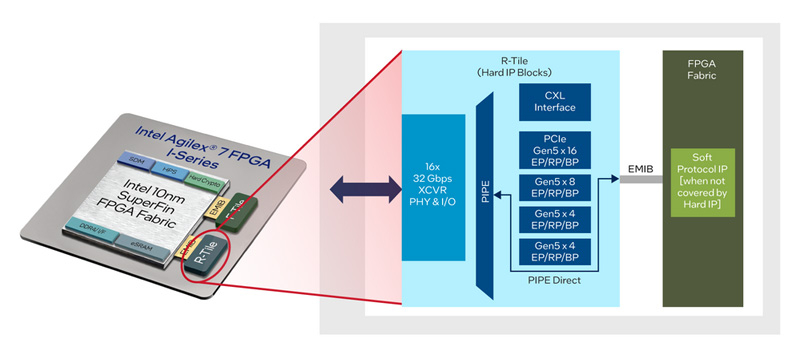

Intel выпустила первые FPGA Agilex 7 с поддержкой PCIe 5.0 и CXLКорпорация Intel в ходе суперкомпьютерной конференции ISC 2023 сообщила о начале производства программируемых вентильных матрицах (FPGA) семейства Agilex 7, предназначенных для ускорения выполнения различных задач, связанных с обработкой данных. Часть семейства Agilex 7 были анонсирована в марте нынешнего года. Решения имеют гетерогенную многокристальную архитектуру, в центре которой находится микросхема FPGA, соединённая с трансиверами посредством моста Intel Multi-Die Interconnect Bridge (EMIB). Каждый чиплет (в Intel их называют «плитками») отвечает за выполнение определённых функций. Intel приступила к выпуску версий Agilex 7, в состав которых входит «плитка» R-Tile. Она включает блоки PCIe 5.0 x16 и CXL 1.1/2.0, обеспечивая высокую гибкость при использовании в сетях передачи данных, в составе облачных платформ, ЦОД, систем НРС и пр. Достигается быстродействие до 32 GT/s в расчёте на одну линию. При производстве применятся 10-нм технология.

Источник изображений: Intel  Отмечается, что настраиваемая и масштабируемая архитектура Agilex 7 позволяет заказчикам быстро разворачивать платформы в соответствии со своими специфичными потребностями. Это обеспечивает оптимальную производительность дата-центров и позволяет сократить затраты. Изделия Agilex 7 могут применяться в серверах на основе процессоров Intel Xeon Sapphire Rapids. |

|