Материалы по тегу: morello

|

22.06.2024 [00:05], Алексей Степин

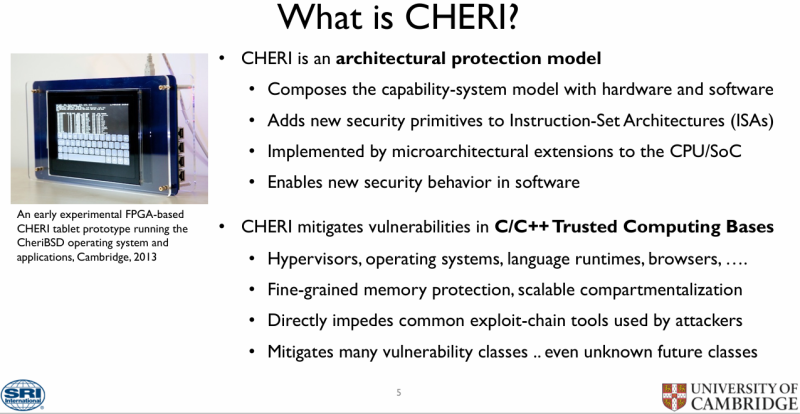

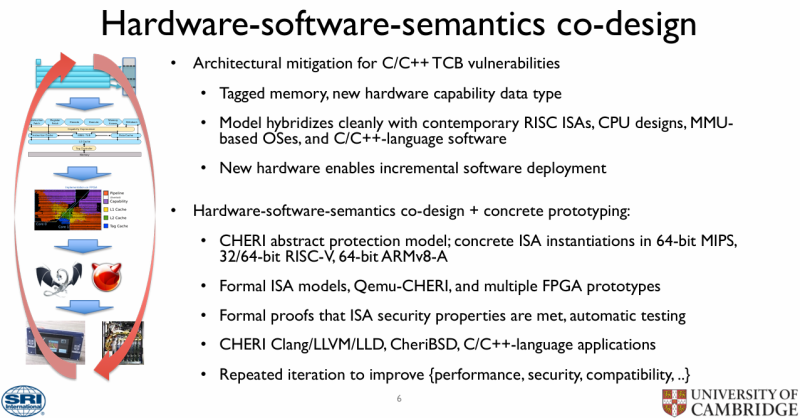

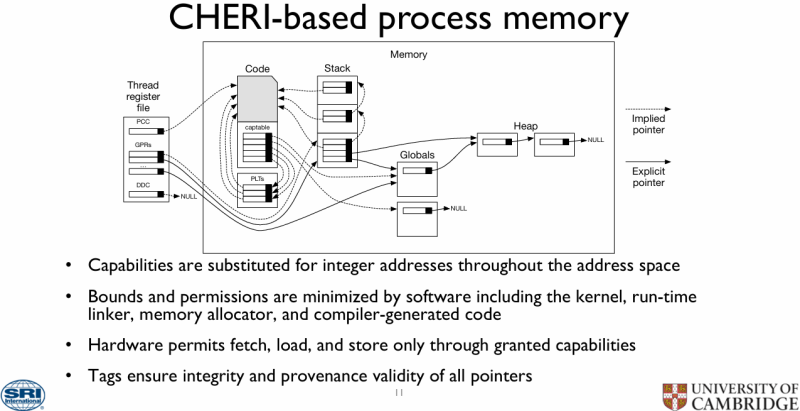

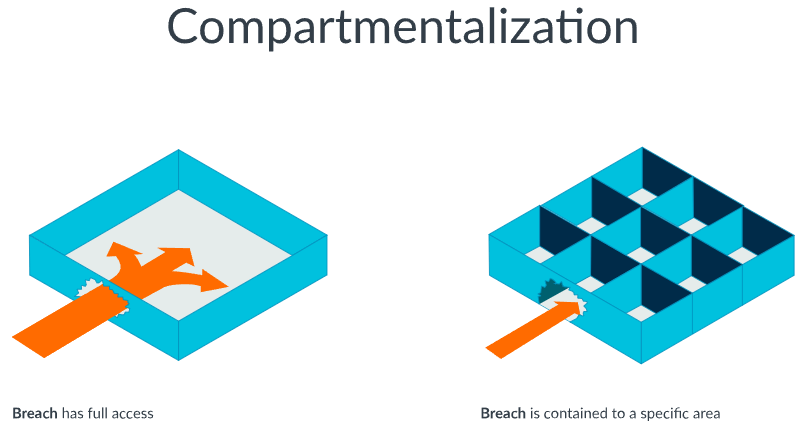

Альянс CHERI будет продвигать технологию надёжной защиты памяти от атак — первой её могут получить процессоры RISC-VВ современных процессорах немало возможностей для атак связано с особенностями работы современных подсистем памяти. Для противостояния подобным угрозам Capabilities Limited, Codasip, FreeBSD Foundation, lowRISC, SCI Semiconducto и Кембриджский университет объявили о создании альянса CHERI (Capability Hardware Enhanced RISC Instructions). Целью новой организации должна стать помощь в стандартизации, популяризации и продвижении на рынок разработанных Кембриджским университетом совместно с исследовательским центром SRI International процессорных расширений, позволяющих аппаратно реализовывать механизмы защиты памяти, исключающие целый ряд потенциальных уязвимостей, например, переполнение буфера или некорректная работа с указателями. Сама технология имеет «модульный» характер. Она может применяться выборочно для защиты функций от конкретных атак и требует лишь весьма скромной адаптации кода. Согласно заявлению CHERI Alliance, огромный пул уже наработанного ПО на языках семейств С и C++ может быть легко доработан для серьёзного повышения уровня безопасности. Кроме того, данная технология позволяет реализовать высокопроизводительные и масштабируемые механизмы компартментализации (compartmentalization) и обеспечения минимально необходимых прав (least privilege). Такое «разделение на отсеки» должно защитить уже скомпрометированную систему и не позволить злоумышленнику развить атаку, даже если он воспользовался ранее неизвестной уязвимостью. Технологии, предлагаемые альянсом CHERI, хорошо проработаны — их развитие идёт с 2010 года, а актуальность массового внедрения подобных решений за прошедшее время успела лишь назреть. Однако для успеха данной инициативы потребуется широкое содействие со стороны индустрии как аппаратного обеспечения, так и программного. Участники альянса настроены оптимистично, однако в их число пока не входит ни один из крупных разработчиков CPU, в частности, Arm. В настоящее время главной архитектурой для приложения своих усилий они видят RISC-V, о чём свидетельствует документация на CHERI ISAv9. Впрочем, черновой вариант расширений имеется и для x86-64. Сама Arm этого оптимизма не разделяет. Компания имеет за плечами пятилетний опыт разработки проекта Morello, основанному на идеях CHERI, но, по словам представителя Arm, процесс тестирования прототипов защищённых систем выявил ряд ограничений, пока препятствующий их широкому распространению на рынке. Тем не менее, работы над платформой Morello будут продолжены. При этом буквально на днях для Arm-процессоров была выявлена атака TikTag, направленная на обход механизма защиты памяти Memory Tagging Extensions (MTE).

24.01.2022 [20:09], Алексей Степин

Arm выпустила прототип платы с процессором повышенной безопасности MorelloВ современном мире процессоров уже никого не удивляет нахождение очередной уязвимости, а иногда тропинкой для злоумышленника становятся технологии, изначально призванные повысить уровень безопасности. Ряд исследователей небезосновательно считает, что «заплатками» отделаться не получится и надо менять глубинные принципы, лежащие в основе процессорных архитектур. Один из таких проектов, развиваемый с 2010 года усилиями SRI International и Кембриджского университета — это CHERI. В 2019 к нему присоединилась Arm, недавно представившая первый прототип платы с процессором Morello, который базируется на двух ключевых принципах, заложенных в CHERI — масштабируемая компартментализация и тонко настраиваемая защита содержимого памяти. Оба принципа реализованы аппаратно и сами по себе не новы.

Изображения: Arm По сути речь идёт о расширении стандартного набора инструкций, с помощью которого даже написанное с использованием языков, позволяющих относительно легко сделать ошибки при работе с памятью (а это обычно C/C++), ПО можно заставить работать без образования серьёзных дыр в защите. Тщательная компартментализация (т.е. разделение) кода ОС и приложений хотя и не исключает наличие уязвимостей, но серьёзно ограничивает область возможного нанесения вреда.  В частности, любая инструкция типа load/store и любая операция выборки должны быть авторизованы на аппаратном уровне со стороны процессора. Разумеется, это не высокоуровневая защита, а скорее набор базовых блоков для построения таковой. Принцип компартментализации ещё проще: если в классической архитектуре взломщик может получить контроль над всей системой, то в изолированных друг от друга ОС и приложениях, он лишь проникнет в одну из множества небольших «ячекк», а его действия послужат сигналом для защитных механизмов.

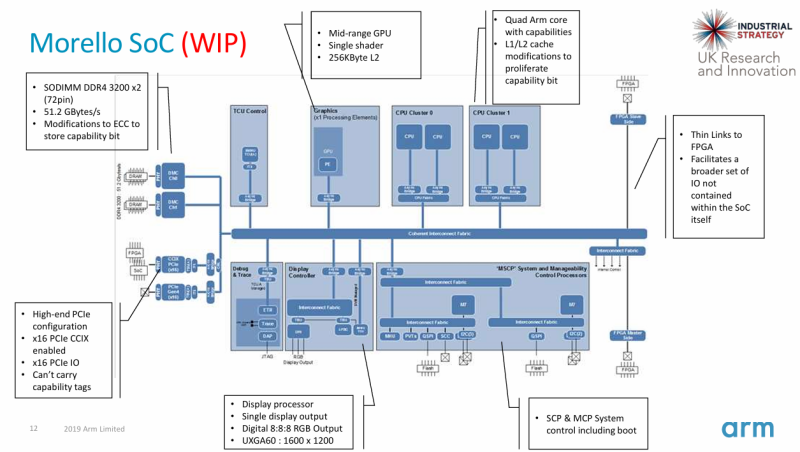

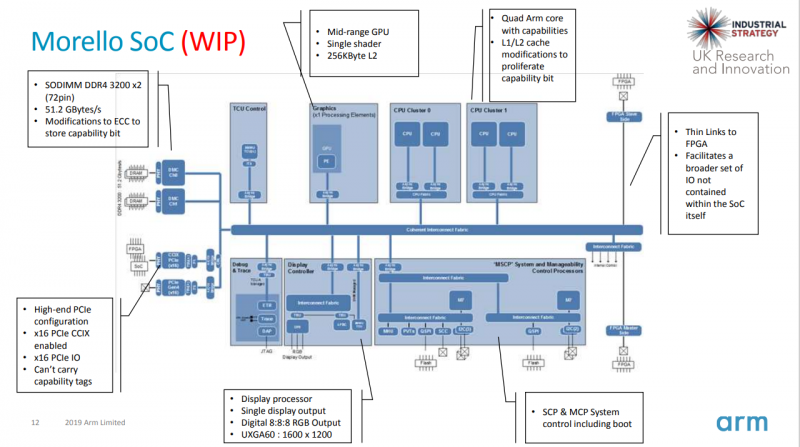

Блок-схема Arm Morello Arm Morello — первый чип на базе CHERI. Текущая аппаратная реализация использует модифицированные ядра Neoverse N1 (ARMv8.2) с частотой 2,5 ГГц. Первые платы с новым процессором предназначены таким IT-гигантам как Google и Microsoft, а также заинтересованным партнёрам образовательным учреждениям. На текущий момент разработчики предлагают модифицированное ядро FreeBSD, часть стандартных UNIX-программ, а также некоторые другие приложения. С появлением готовых плат и процессоров процесс адаптации ПО должен значительно ускориться. |

|