В современных процессорах немало возможностей для атак связано с особенностями работы современных подсистем памяти. Для противостояния подобным угрозам Capabilities Limited, Codasip, FreeBSD Foundation, lowRISC, SCI Semiconducto и Кембриджский университет объявили о создании альянса CHERI (Capability Hardware Enhanced RISC Instructions).

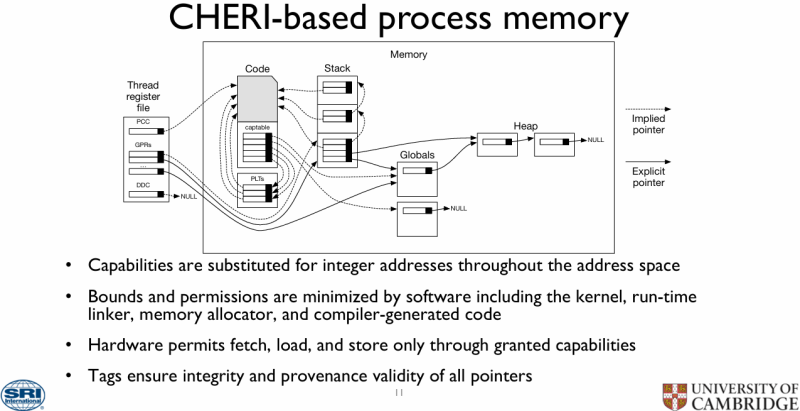

Целью новой организации должна стать помощь в стандартизации, популяризации и продвижении на рынок разработанных Кембриджским университетом совместно с исследовательским центром SRI International процессорных расширений, позволяющих аппаратно реализовывать механизмы защиты памяти, исключающие целый ряд потенциальных уязвимостей, например, переполнение буфера или некорректная работа с указателями.

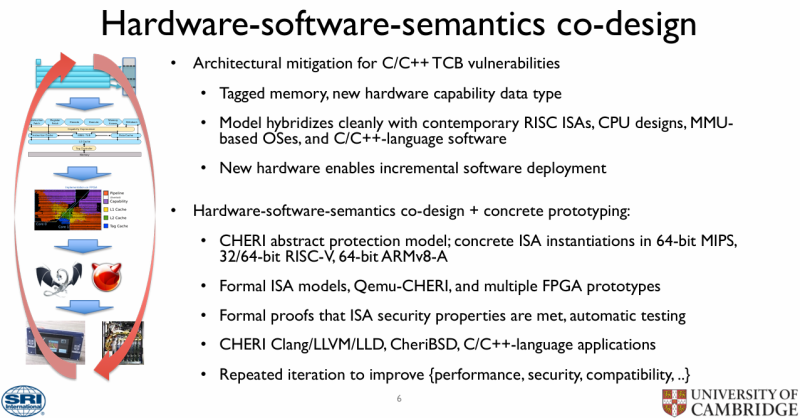

Сама технология имеет «модульный» характер. Она может применяться выборочно для защиты функций от конкретных атак и требует лишь весьма скромной адаптации кода. Согласно заявлению CHERI Alliance, огромный пул уже наработанного ПО на языках семейств С и C++ может быть легко доработан для серьёзного повышения уровня безопасности.

Кроме того, данная технология позволяет реализовать высокопроизводительные и масштабируемые механизмы компартментализации (compartmentalization) и обеспечения минимально необходимых прав (least privilege). Такое «разделение на отсеки» должно защитить уже скомпрометированную систему и не позволить злоумышленнику развить атаку, даже если он воспользовался ранее неизвестной уязвимостью.

Технологии, предлагаемые альянсом CHERI, хорошо проработаны — их развитие идёт с 2010 года, а актуальность массового внедрения подобных решений за прошедшее время успела лишь назреть. Однако для успеха данной инициативы потребуется широкое содействие со стороны индустрии как аппаратного обеспечения, так и программного.

Участники альянса настроены оптимистично, однако в их число пока не входит ни один из крупных разработчиков CPU, в частности, Arm. В настоящее время главной архитектурой для приложения своих усилий они видят RISC-V, о чём свидетельствует документация на CHERI ISAv9. Впрочем, черновой вариант расширений имеется и для x86-64.

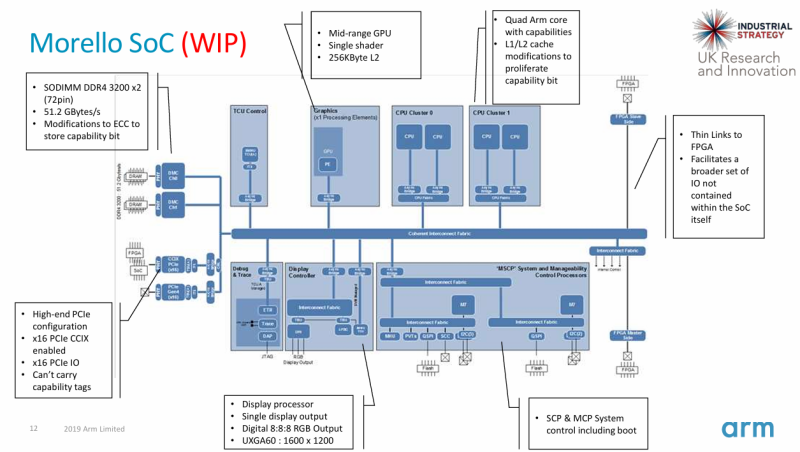

Сама Arm этого оптимизма не разделяет. Компания имеет за плечами пятилетний опыт разработки проекта Morello, основанному на идеях CHERI, но, по словам представителя Arm, процесс тестирования прототипов защищённых систем выявил ряд ограничений, пока препятствующий их широкому распространению на рынке. Тем не менее, работы над платформой Morello будут продолжены. При этом буквально на днях для Arm-процессоров была выявлена атака TikTag, направленная на обход механизма защиты памяти Memory Tagging Extensions (MTE).

Источник: