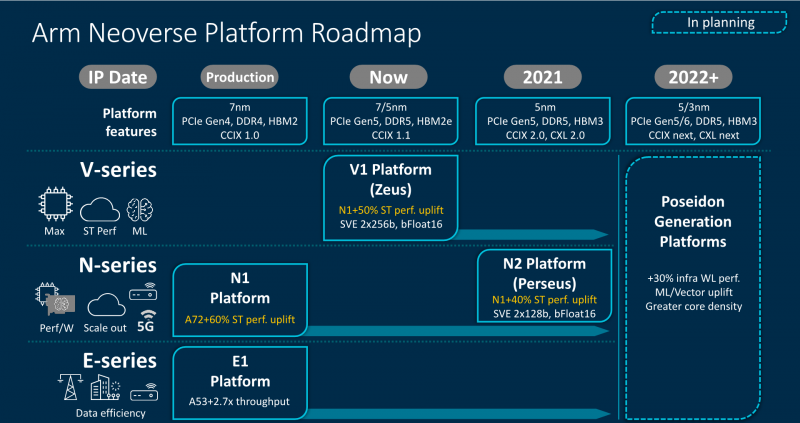

Компания Arm объявила о расширении своего портфолио серверных решений семейства Neoverse, представив сразу два варианта платформы. Новая серия V и её первенец V1 под кодовым именем Zeus вместе с N2 (Perseus) получат поддержку SIMD-расширений SVE и формата bfloat16, а также интерфейсы PCIe 5.0, DDR5 и HBM.

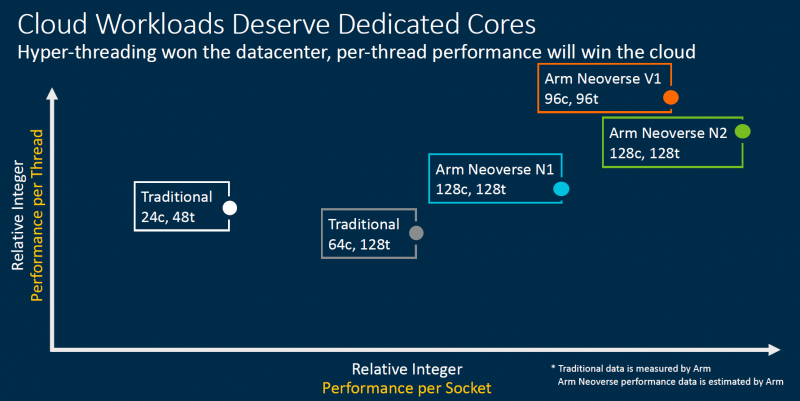

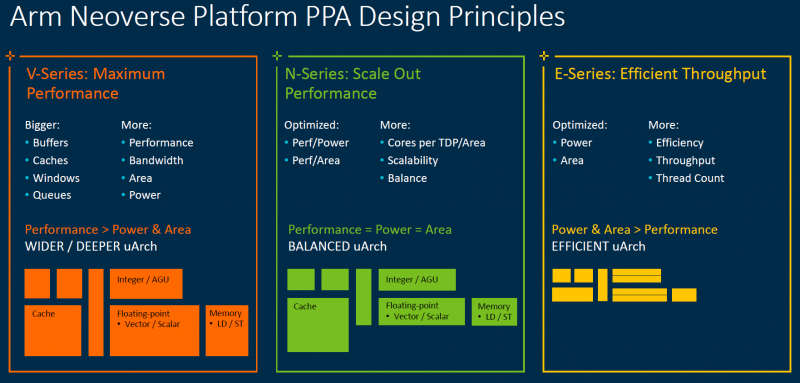

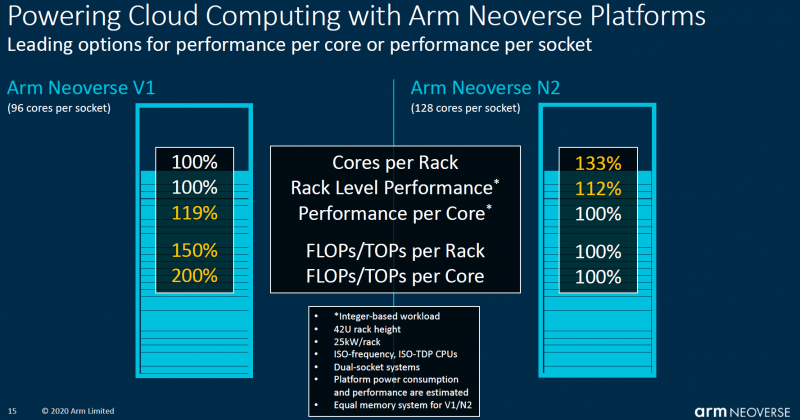

Однако отличия между ними весьма существенны. В Neoverse V1 в отличие от N2 Arm отказывается от традиционной оптимизации сразу по трём направлениям — энергопотребление, производительность и площадь кристалла — и делает упор на мощность. Вероятно, основой для них станут вариации Cortex-X1. Эти чипы будут потреблять больше энергии и будут физически больше, но взамен предложат значительное увеличение размеров буферов, кешей, окон и очередей. Показатель IPC для одного потока будет увеличен на впечатляющие 50% в сравнении с Neoverse N1.

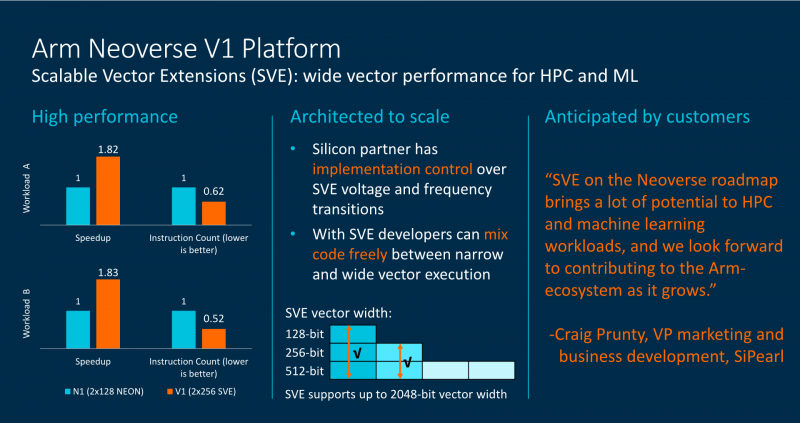

А новые техпроцессы 5 и 7 нм позволят повысить частоты будущих процессоров. Так что они потенциально смогут соревноваться с грядущими платформами x86-64 не только по показателю производительность на Ватт, но и в чистой производительности. Поспособствует этому и долгожданное официальное появление векторных инструкций Scalable Vector Extension (SVE) в составе самого ядра. Их отличительной чертой (от SSE/AVX) является нефиксированная ширина — производители конкретных SoC могут реализовать поддержку от 128 до 2048 бит с шагом в 128 бит. При этом SVE-код будет работать на любом из них, просто скорость обработки данных будет разной.

Конкретно в V1 Arm заложила два блока SVE-256. Это явно хуже пары SVE-512 в Fujitsu A64FX, единственном «кремнии», который уже поддерживает новые инструкции, но всё равно в два раза лучше, чем у N1 с двумя «старыми» 128-бит NEON. Так что мы вполне можем увидеть в будущем ориентированные на высокопроизводительные вычисления решения от других компаний. Этому поспособствует и поддержка памяти HBM2e. Опять-таки, в A64FX она была нужна именно для того, чтобы SVE-блоки не «голодали». Кроме того, обновлённые спецификации SVE включают и поддержку формата bfloat16, актуального для нейронных сетей.

Arm Neoverse V1 формально доступен уже сейчас. Первыми процессорами на базе этой архитектуры должны стать 72-ядерные SiPearl Rhea, которые вместе с другими чипами, уже на базе открытой архитектуры RISC-V, лягут в основу будущих европейских суперкомпьютеров. Таким образом Евросоюз надеется получить большую независимость от технологий США. Впрочем, объявленная сделка между NVIDIA и Arm может расстроить эти планы. Следующим крупным лицензиатом V1 может стать Ampere, которая готовится выпустить в 2022 году процессоры Siryn.

Что касается архитектуры Neoverse N2, то она появятся уже в следующем году, а лицензирование начнётся в конце этого. Она также получит поддержку SVE и bfloat16, но в виде двух 128-бит блоков. Будет внедрена поддержка HBM3, CXL 2.0 и CCIX 2.0. В N2 Arm придерживается своего традиционного подхода, так что прирост IPC в однопотоке составит «всего лишь» до 40% в сравнении с N1, но при этом сохранятся те же уровень энергопотребления и площадь ядра. Можно предположить, что основной для неё станет Cortex-A78.

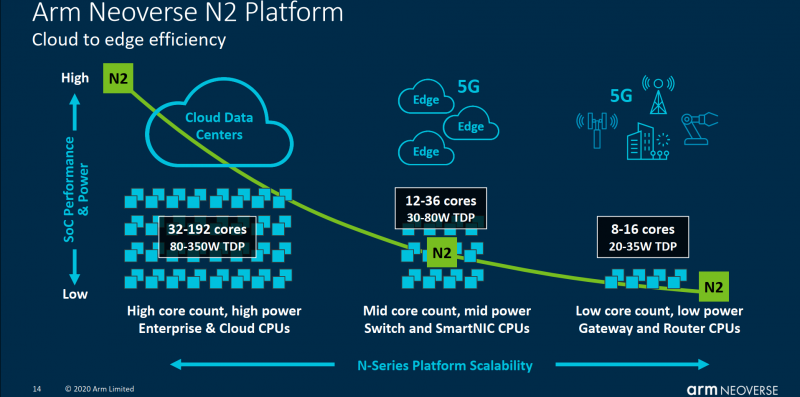

Именно N2 должна стать наиболее массовой платформой благодаря масштабируемости. Arm видит различные варианты дизайнов будущих SoC. От 8 до 16 ядер с TDP 20-35 Вт пойдут в экономичные решения на самой границе сети, варианты на 12-36 ядер с TDP от 30 до 80 Вт могут стать основой периферийных вычислений, а сборки с числом ядер от 32 до 192 и с TDP от 80 до 350 Вт займут место в мощных серверах, включая облачные. Пока что единственным более-менее массовым решением на базе Neoverse N1 владеет Amazon — в мае в AWS появились инстансы на базе 64-ядерных Graviton2.

После 2022 года выйдет следующее поколение Neoverse под кодовым именем Poseidon. Про него пока говорится в общих чертах, что оно станет производительнее на 30%, получит улучшения по части векторных инструкций и машинного обучения, обзаведётся поддержкой будущих версий CCIX и CXL, а также предложит более плотную упаковку ядер.

Источники: