Материалы по тегу: эльбрус

|

07.01.2022 [00:05], Алексей Степин

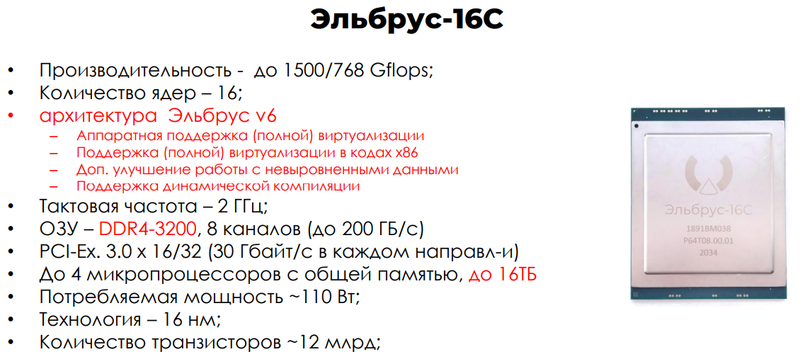

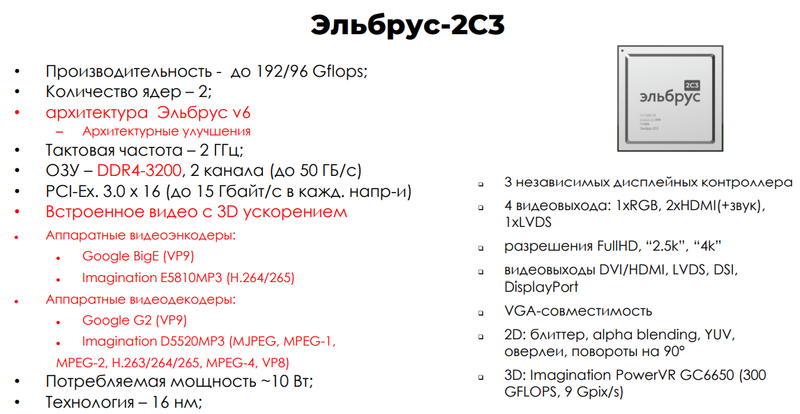

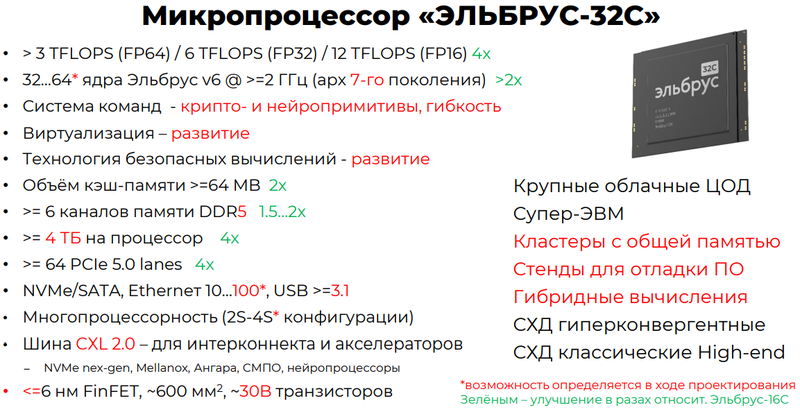

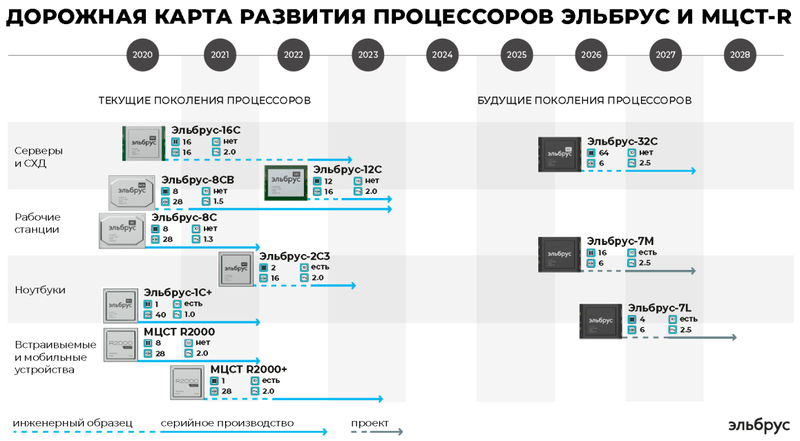

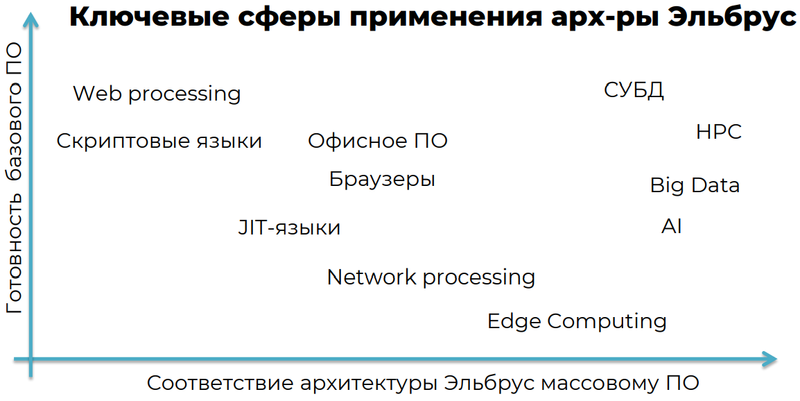

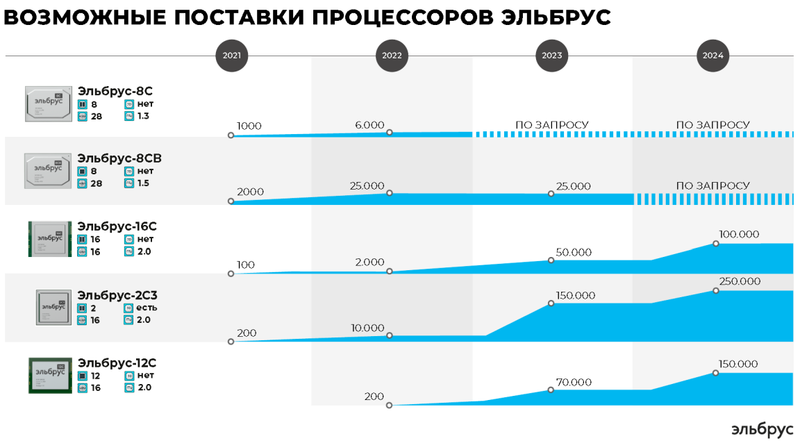

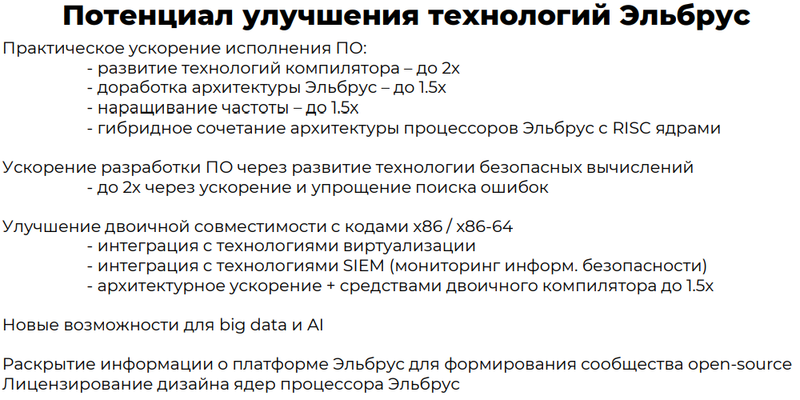

Серийное производство Эльбрус-16С и 2С3 начнётся в этом годуРоссийские процессоры Эльбрус, разрабатываемые компанией МЦСТ, вызывают немало споров вокруг самой архитектуры и доступности изделий на её основе. Но платформа продолжает жить и развиваться, несмотря на все трудности. Для всех процессоров разработан типовой ряд модулей и системных плат, от простых вариантов с одним CPU до высокоплотных четырёхсокетных. Есть решения и для обычных настольных ПК, а также модули для встраиваемых и терминальных систем. В конце прошлого года на очередной партнёрской конференции МЦСТ были опубликованы новые доклады, в том числе, освещающие изменения в ситуации с доступностью процессоров и решений на их основе. А изменений этих немало. Во-первых, окончательно устаревшими можно признать чипы Эльбрус-8. Им на смену пришла усовершенствованная версия Эльбрус-8СВ. Крупная партия этих чипов в настоящее время уже получена и находится в процессе таможенного оформления. Этот чип, напомним, лишён целого ряда недостатков, присущих Эльбрус-8С.  Однако 28-нм техпроцесс себя исчерпал, и в 2022 году на смену придут 16-нм процессоры Эльбрус-16С, Эльбрус-12С и Эльбрус-2С3. В их основу легла новая, шестая версия VLIW-архитектуры МЦСТ. Она сопровождается отказом от уже устаревшей и медленной схемотехники подсистем ввода-вывода, реализованной в предыдущем поколении Эльбрус на базе моста КПИ-2 и переходом на интегрированный контроллер PCI Express.  Старший 16-ядерный вариант получил 8-канальный контроллер DDR4-3200, что вполне отвечает требованиям современности. Планка максимального объёма оперативной памяти поднята до 16 Тбайт в четырёхпроцессорной системе (4х4 Тбайт). Благодаря новому техпроцессу удалось удержать в приличных рамках теплопакет, выросший с 80 до 110 ватт при вдвое большем количестве ядер.  Современный серверный процессор немыслим без виртуализации, и в новых решениях МЦСТ её аппаратная поддержка реализована в полном объёме, в том числе, для кода x86. Появилась поддержка динамической компиляции, дополнительно оптимизирована работа с невыровненными данными. Но главное, что образцы Эльбрус-16С и 2С3 получены и успешно прошли тесты. Подготовлена вторая ревизия, данные по ней уже переданы контрактному производителю.  Младший Эльбрус-2С3 в дополнение к интегрированному GPU получил продвинутый набор аппаратных кодеков, который включает VP9 и H.264/H.265. Процессор пойти в серию в течение этого года, а рабочие прототипы систем на его базе уже есть. 12-ядерный Эльбрус-12С наиболее интересный, как платформа для рабочих станций разработки ПО для данной архитектуры, пока ждёт второй ревизии, которая должна быть готова в течение первой половины 2022 года.  Не забывает МЦСТ и о корнях — разработке архитектур на базе SPARC. Образцы процессора R2000+ также получены и прошли инженерные тесты. Это чип, ориентированный на сверхэкономичные системы — его теплопакет составляет всего 5 Ватт, но при этом он имеет встроенное графическое ядро с функциями 3D-ускорения.  Что касается приверженности самой архитектуре VLIW, то МЦСТ продолжает настаивать на преимуществах явного параллелизма команд, осознавая, разумеется, необходимость качественного компилятора. Интерес представляет диаграмма применимости архитектуры Эльбрус: она не очень подходит для веб-задач и скриптовых языков, а лучше всего, по мнению разработчиков, раскрывает себя в задачах HPC/Big Data, СУБД и ИИ-системах.  Что касается внедрения, то серверы на базе процессоров Эльбрус активно внедряются в государственных учреждениях: ЦОД для ГИС «Мир» содержит порядка 200 серверов, а МВД России недавно закупило более 400 серверов для автоматизированной системы фиксации нарушений. РЖД внедряет тонкие клиенты на базе Эльбрус, а также использует его в системах автоматики управления стрелочным хозяйством. Силами Ростелеком создано первое облако на базе Эльбрус-8С/СВ.  Но, пожалуй, наибольшего успеха в импортозамещении добились энергетики: удалось разработать и внедрить самый широкий спектр решений на базе Эльбрус, от систем автоматики для подстанций до полноценной АСУ ТП «ПАК МАРС» для компании Россети. В последнем случае Эльбрус используется во всех компонентах, от клиентских рабочих мест до серверов и СХД.  С точки зрения программной экосреды наиболее интересна система двоичной трансляции, позволяющая запускать ПО, разработанное для х86-64, которое затем постепенно можно оптимизировать и переводить в «родной режим». Начаты работы по внедрению механизмов динамической оптимизации на базе LCC и LLVM. Также стоит отметить появление поддержки LLVM 13-ой ветки и бета-версию систем виртуализации на базе KVM + QEMU + libvirt.  МЦСТ заботится о разработчиках: первые 100 экземпляров плат на базе Эльбрус-16С и 2С3 уже разосланы партнёрам для реализации пилотных проектов. Компания готовится сертифицировать дизайн-центры и контрактные производства, а также сообщает о том, что появились первые дистрибьюторы, работающие с продукцией на базе Эльбрус.  Весьма интересны как планы МЦСТ по выпуску новых процессоров на базе VLIW-архитектуры седьмого поколения, так и данные относительно нововведений в этой архитектуре. В планах создание процессора с числом ядер до 64 и с системой команд, включающей крипто- и нейропримитивы, продвинутыми средствами виртуализации и безопасных вычислений, и, что немаловажно, поддержкой прогрессивного универсального стандарта CXL 2.0.  Запланировано использование 6-нм техпроцесса, а также выпуск чипов с меньшим количеством ядер для рабочих станций и ноутбуков. Также рассматривается возможность создания гибридного процессора, сочетающего ядра Эльбрус и RISC-V. Такой чип с учётом поддержки бинарной трансляции сможет претендовать на звание самого универсального ЦП в мире.  Ознакомиться полнее с материалами конференции можно на сайте МЦСТ. В целом, архитектура Эльбрус выглядит живой и развивающейся, решения на базе уже освоенных 8-ядерных процессоров активно внедряются в России, а более новые 12 и 16-ядерные CPU гораздо лучше соответствуют современным требованиям. Что касается Эльбрус-32С, то это амбициозный проект, в котором сочетаются как новейшие технологии (DDR5 и CXL 2.0), так и уникальные архитектурные особенности.

14.12.2021 [19:41], Алексей Степин

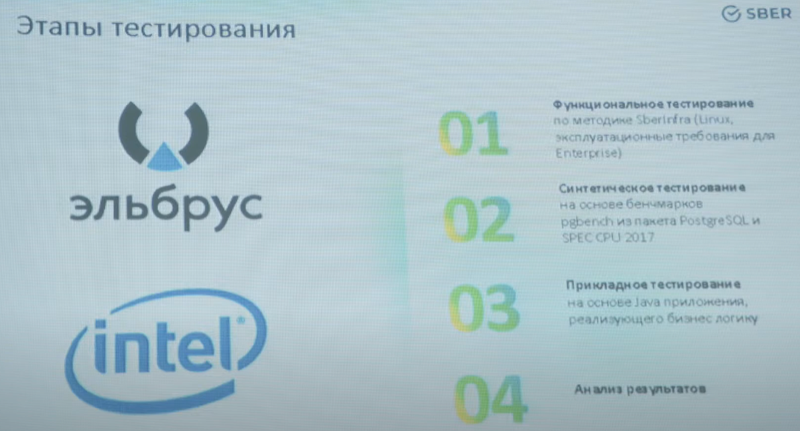

Серверы на базе «Эльбрус» не прошли тесты Сбербанка, но не всё потеряноВ рамках программы импортозамещения СберТех провёл тестирование серверов на базе процессоров Эльбрус-8С. По результатам системы признаны работоспособными, но не отвечающими предъявляемым требованиям по целому ряду параметров. Все пожелания и замечания переданы МЦСТ, разработчику Эльбрус. Банковские информационные системы — критически важная часть любого государства. Поэтому неудивительно стремление использовать в них решения собственной разработки, дабы меньше зависеть от чужих чипов и серверов. Примеры Huawei это подтверждают, но в данной заметке речь пойдёт не о китайских процессорах, а о российских. Лаборатория СберТех провела полноценное тестирование серверов на базе процессоров Эльбрус-8С, результаты которого, к сожалению, трудно назвать удовлетворительными.

Фото: МЦСТ Это первое полномасштабное испытание процессоров Эльбрус в «полевых условиях», то есть, на уровне реальных серверов и задач, которые эти серверы должны выполнять. В испытаниях приняли участие платформы с двумя и четырьмя чипами Эльбрус-8С (VLIW, 8C/8T, 1,3 ГГц, 16 Мбайт L3-кеш, 70 Вт TDP, 28 нм). В качестве оппонентов выступили «типичные системы» на базе Intel Xeon Gold 6230 (x86-64, Cascade Lake-SP, 20C/40T, 2,1-3,9 ГГц, 27,5 Мбайт кеш, 125 Ватт TDP, 14 нм), которых в Сбере тысячи и тысячи.

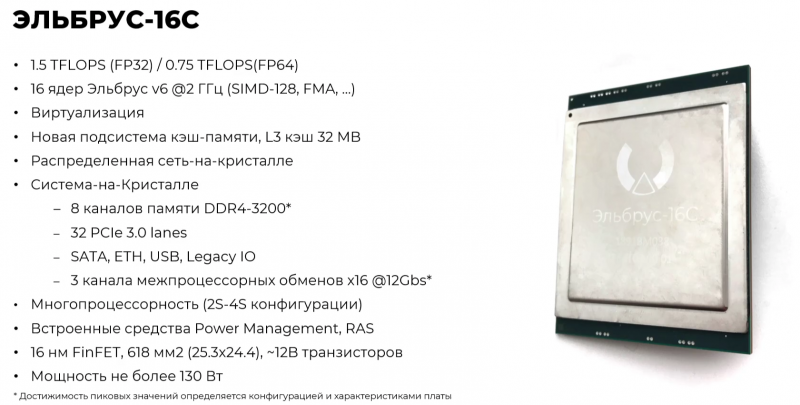

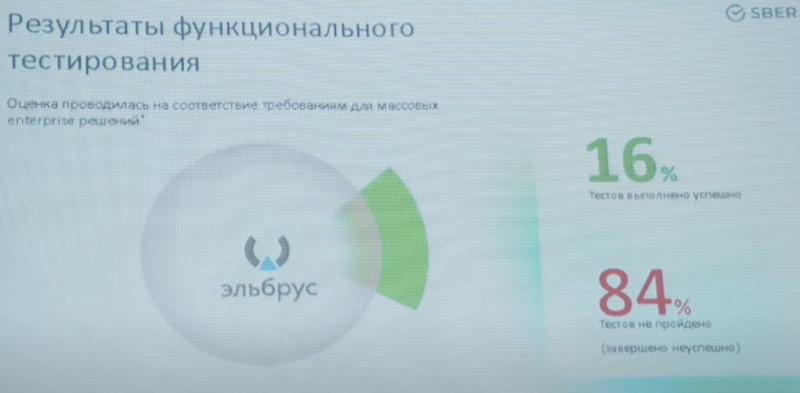

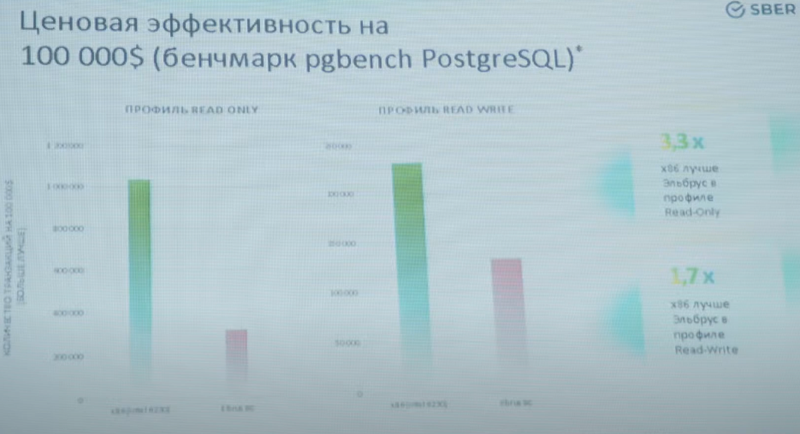

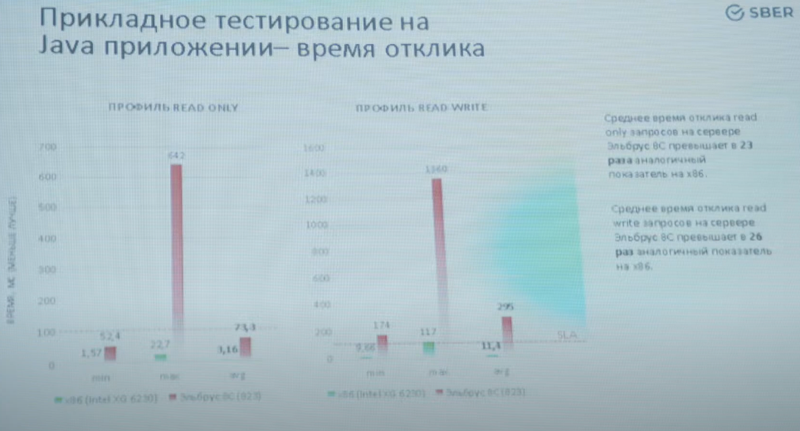

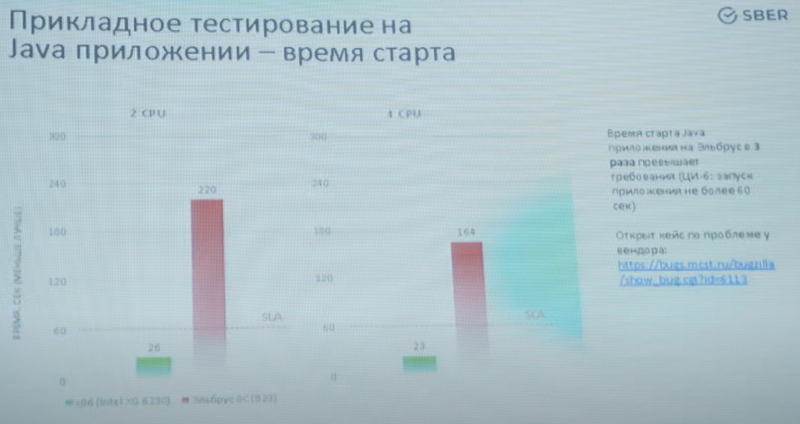

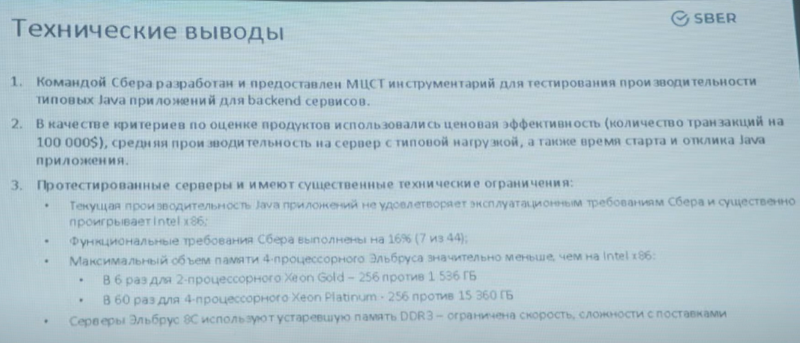

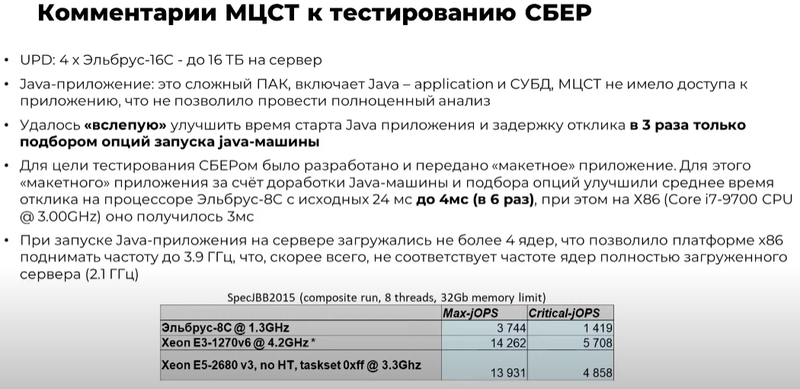

Изображения: YouTube/ElbrusTV По итогам тестирования серверы признаны работоспособными, но показавшими неудовлетворительный уровень производительности. Озвучены основные выводы: «мало памяти, медленная и устаревшая память, мало ядер, низкая тактовая частота». Особенно низкой оказалась производительность в приложениях, использующих Java.  Если в тестах PGbench/PostreSQL Xeon опередил Эльбрус в 1,7-3,3 раза, то в тестах на время отклика Java-приложения разница составила 23-26 раз. Запуск приложения, который по нормативам СберТеха должен укладываться в 60 секунд, занял у серверов Эльбрус 220 секунд в двухпроцессорном варианте и 164 секунды — в четырёхпроцессорном.  Кроме того, в рамках стандартных спецификаций компании системы на базе Эльбрус-8С смогли пройти всего по 7 параметрам из 44 предъявляемых. Если отсутствие монтажных стоечных рельсов можно отнести к «мелким претензиям», которые легко решаются, то отсутствие системы удалённого управления — недоработка весьма серьёзная, поскольку затраты на увеличение штата ИТ-специалистов окажутся непомерно велики.  Стоит, однако, отметить, что Эльбрус-8С уже устарел в рамках собственной экосистемы: МЦСТ обещает представить на тестирование усовершенствованные варианты серверов на базе Эльбрус-8СВ с более высокой частотой (1,5 против 1,3 ГГц), удвоенной производительностью в операциях над числами с плавающей запятой, а также использующие память DDR4-2400 (до 1 Тбайт на сервер) вместо окончательно устаревшей DDR3-1600. Однако массовые поставки таких серверов при заказе 1-5 тыс. единиц возможны не ранее IV квартала 2022 года при заказе в III квартале 2021 года.  Признана необходимость проведения тестов систем на базе Эльбрус под управлением ОС, сертифицированных ФСТЭК по профилю не ниже ОС.А4 (использование для обработки персональных данных и ГИС). Также отмечена необходимость введения полноценной поддержки технологий виртуализации, а не только контейнеризации.  Отметим также, что МЦСТ успешно завершила разработку Эльбрус-16С, в котором ряд фундаментальных недостатков, присущих процессорам Эльбрус-8С/8СВ успешно устранён. Новый чип будет иметь 16 ядер с возросшей до 2 ГГц частотой, восьмиканальный контроллер памяти DDR4-3200 (до 16 Тбайт на сервер), контроллер 10GbE и интегрированный контроллер PCIe 3.0 (32 линии). Последний снимает серьёзные ограничения по пропускной способности чипов Эльбрус-8C/CB к периферийным устройствам. Также с 8 до 48 Гбайт/с возрастёт скорость межпроцессорного обмена данными.  Представитель МЦСТ отметил, что низкие результаты в Java-тестах отчасти обусловлены «слепым тестированием», в котором разработчикам не были предоставлены данные, необходимые для полноценной оптимизации Java-машины. Простым подбором опций МЦСТ удалось улучшить показатели в три раза, а «макет» оптимизированного приложения СберТеха позволил сократить время отклика с 24 до 4 мс, что практически равнозначно показателям систем на базе процессоров Intel (Core i7-9700, 3 мс).

17.02.2021 [00:43], Игорь Осколков

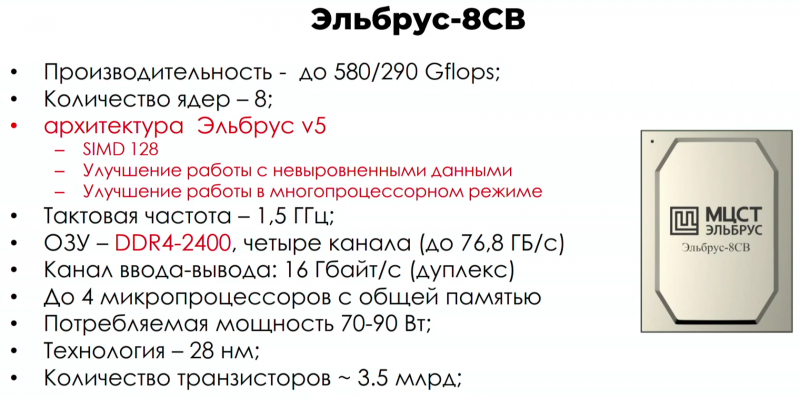

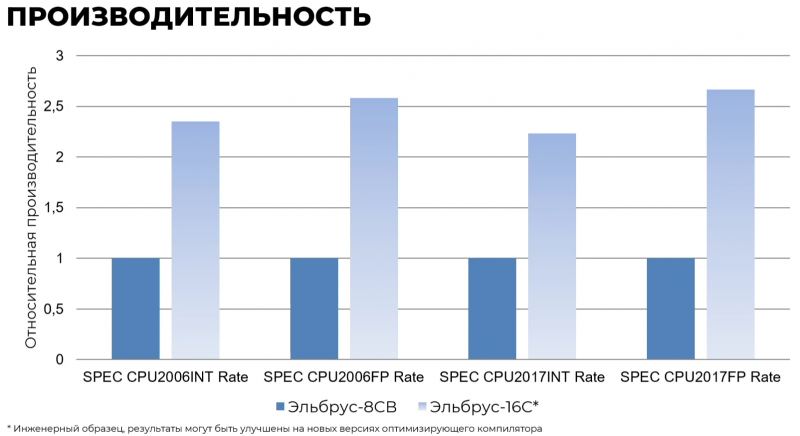

Российские процессоры Эльбрус-16С, Эльбрус-12С и Эльбрус-2С3 получат ядра шестого поколения архитектуры E2KНа мероприятии Elbrus Tech Day компания МСЦТ рассказала о текущих достижениях и планах развития серии российских процессоров Эльбрус. Сейчас наиболее современным CPU этой линейки является Эльбрус-8СВ на базе архитектуры E2K (Эльбрус 2000) пятого поколения, но в ближайшие годы появятся сразу три SoC шестого поколения: Эльбрус-16С, Эльбрус-2С3 и Эльбрус-12С. Эльбрус-8СВ является эволюционным развитием Эльбрус-8. Оба чипа используют 28-нм техпроцесс, но за счёт оптимизаций у 8СВ удалось поднять частоту, что вкупе с поддержкой широких векторных инструкций и более современного стандарта памяти дало двукратный рост теоретической пиковой производительности. Впрочем, для программ, не использующих SIMD, прирост пропорционален увеличению тактовой частоты + они всё равно выигрывают от увеличения скорости работы памяти.

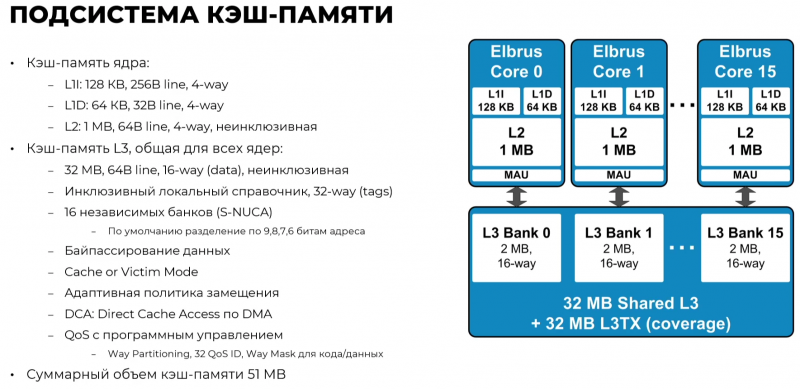

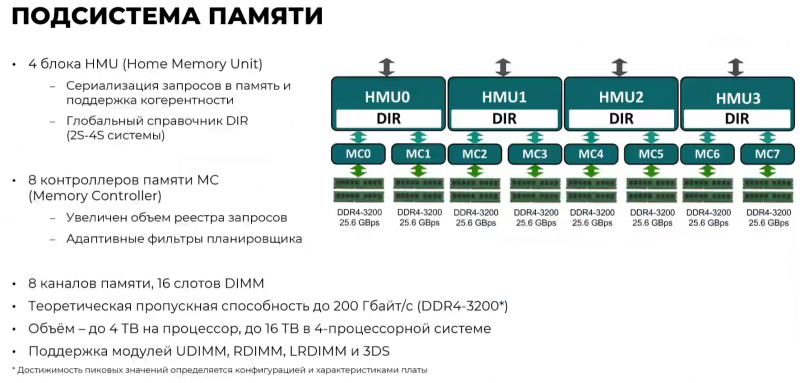

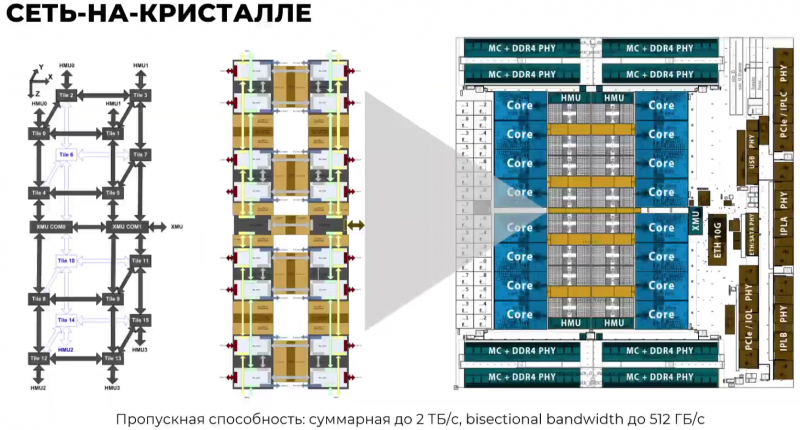

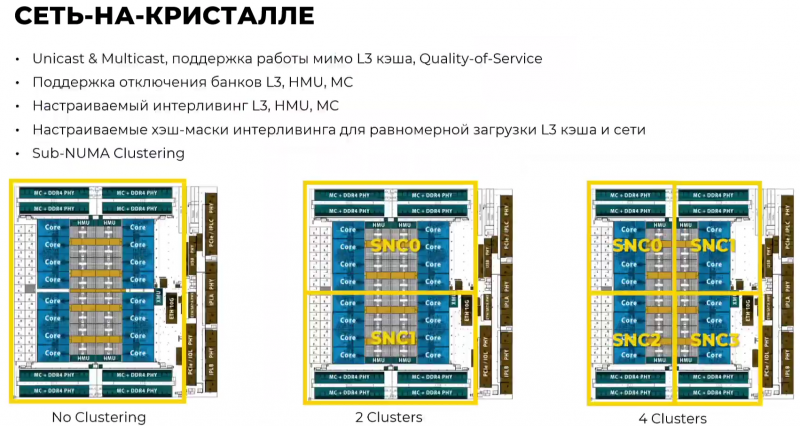

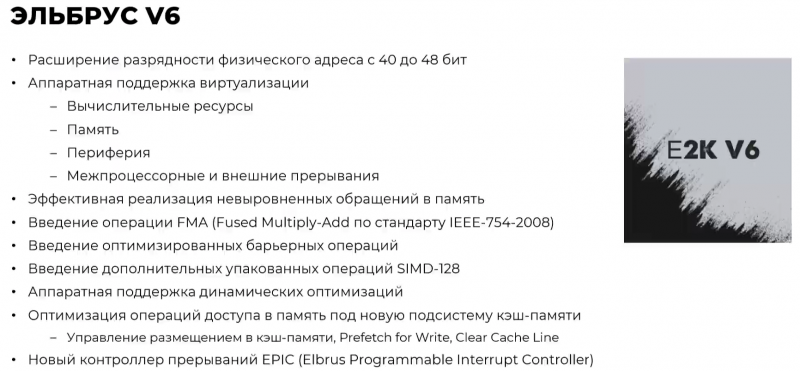

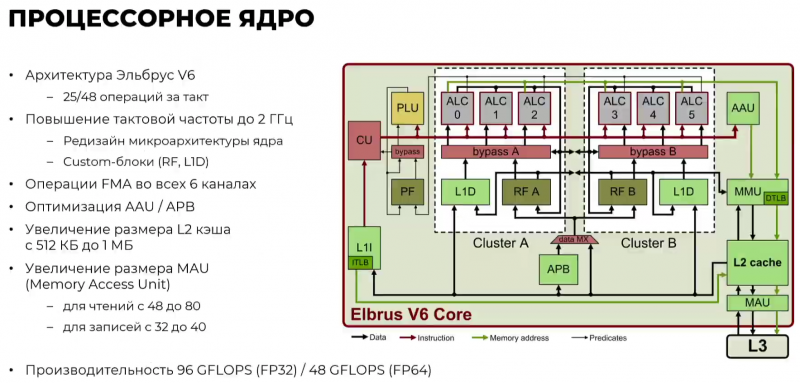

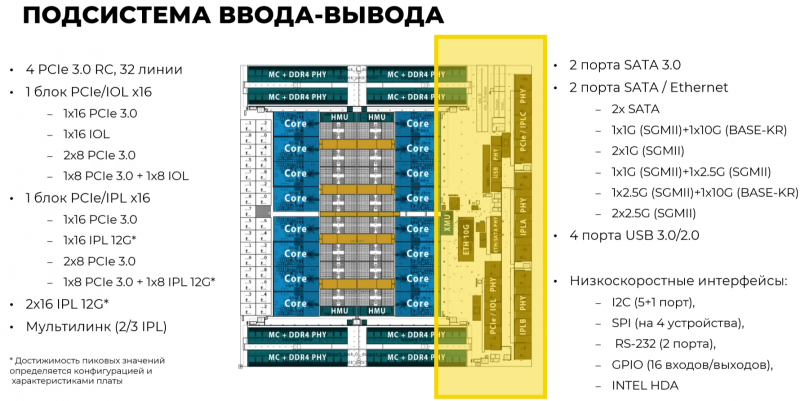

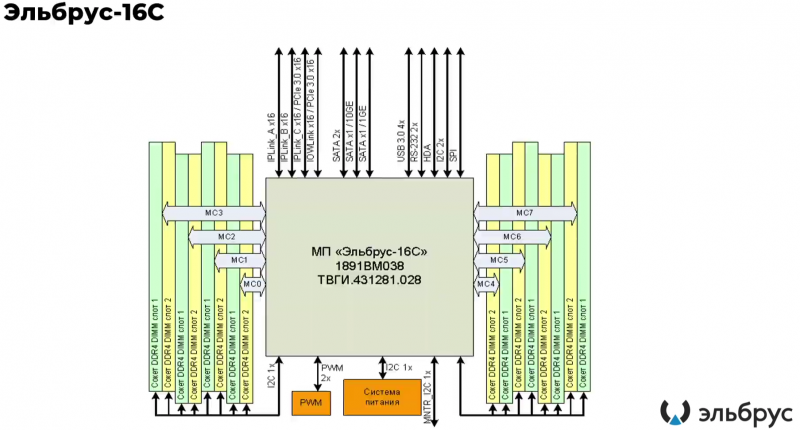

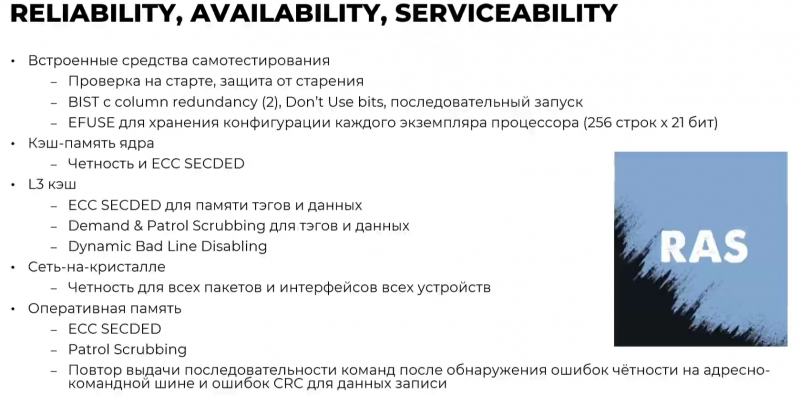

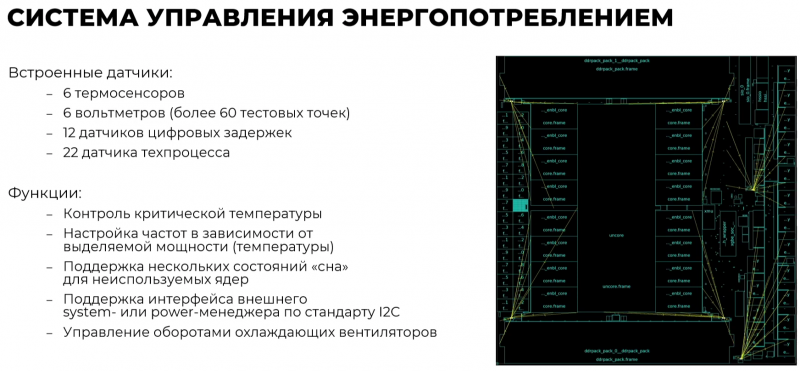

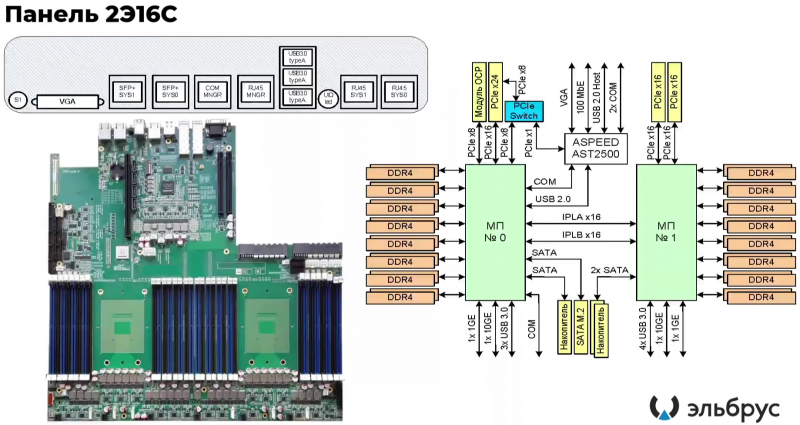

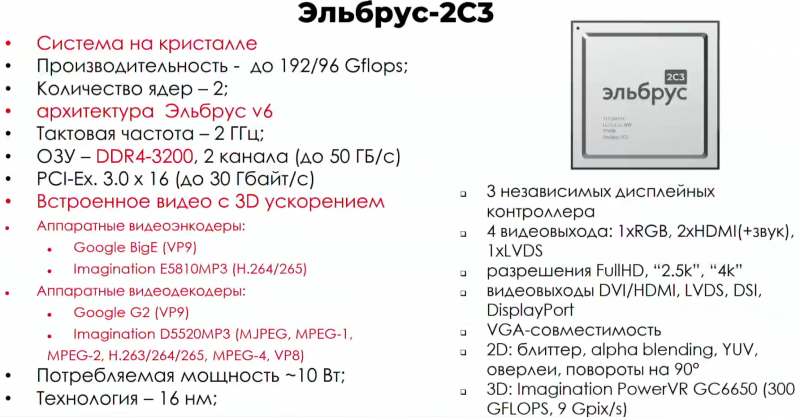

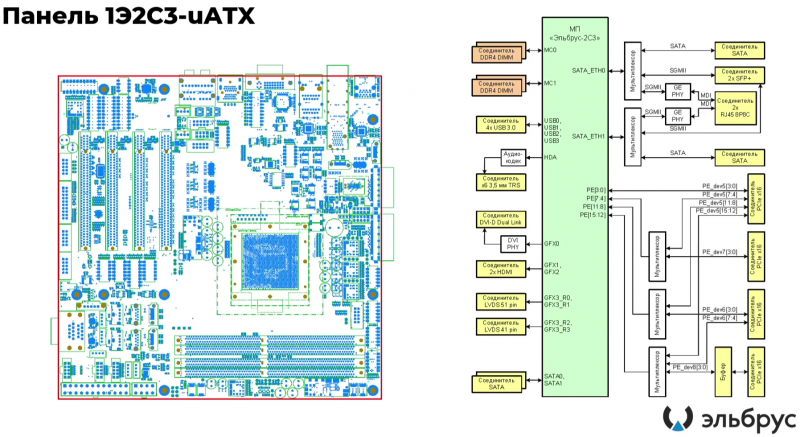

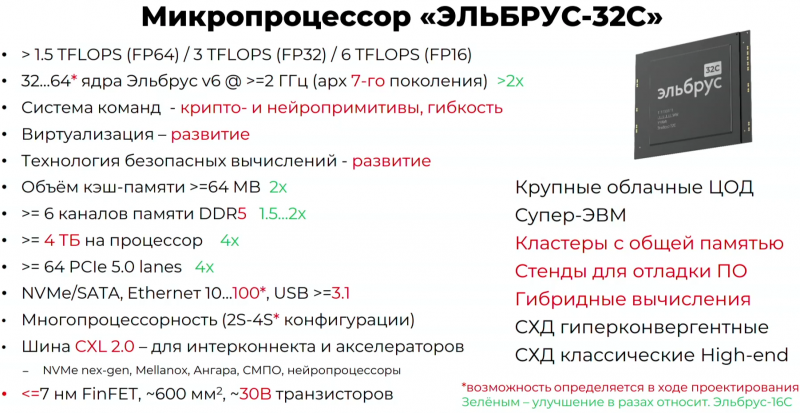

На базе этих и других процессоров компания МЦСТ разрабатывает референсные дизайны материнских плат различных форм-факторов, которые можно лицензировать для дальнейшей кастомизации. Часть партнёров компании разрабатывает собственные материнские платы и изделия на их основе. В скором времени на TSMC будет размещён заказ на изготовление очередной партии Эльбрус-8СВ объёмом 10 тыс. штук. В целом, вокруг уже имеющихся CPU сложилась достаточно заметная экосистема как аппаратных, так и программных продуктов и решений. Следующее поколение процессоров будет разнообразнее. Помимо 16-ядерного Эльбрус-16С, ориентированного на высокопроизводительные серверные системы, будет и модель попроще, которая появится позже остальных — Эльбрус-12С. Этот 12-ядерный CPU рассчитан на серверы начального уровня, а также рабочие станции. А главное отличие от 16С будет в цене. Наконец, ещё один чип, двухъядерный Эльбрус-2С3, ориентирован на мобильные системы, в том числе планшетные компьютеры. Все чипы будут изготавливаться на TSMC по 16-нм техпроцессу FinFET и будут основаны на шестом поколении архитектуры E2K. Строго говоря, это уже не процессоры, а полноценные SoC с интегрированными контроллерами для различной периферии, и для работы им не требуется внешний чип южного моста, как было ранее. В случае Эльбрус-16С площадь кристалла составляет 618 мм2 (25,3 × 24,4 мм), упакован он в корпус HFCBGA4804 с габаритами 63 × 78 мм. Кристалл содержит 12 млрд транзисторов, а его мощность не превышает 130 Вт. Значительная часть изменений в архитектуре коснулась подсистемы памяти. В частности, были увеличены размеры кешей, суммарный объём которых достиг 51 Мбайт: общий для всех L3-кеш 32 Мбайт, увеличенный до 1 Мбайт L2-кеш, L1-кеш для инструкций на 128 Кбайт + L1-кеш данных на 64 Кбайт. Контроллер памяти стал восьмиканальным, получил поддержку модулей DDR4-3200 и 2DPC, что даёт до 4 Тбайт RAM на сокет с суммарной пропускной способностью до 200 Гбайт/с. Первые инженерные образцы Эльбрус-16С, полученные в конце прошлого года, уже выдают в бенчмарке stream скорость порядка 70-80% от максимально возможной. Контроллеры попарно подключены к четырём агентам (HMU), «прикреплённым» к внутренней mesh-шине с пропускной способностью 2 Тбайт/с, объединяющей память и ядра. Чип можно разделить на два или четыре NUMA-домена, что полезно для ряда задач. Одной из таких задач является виртуализация, и в Эльбрус-16С она, наконец, стала полноценной — новые процессоры поддерживают аппаратную виртуализацию практически всех важных ресурсов, в том числе и для режима x86-трансляции, который тоже никуда не делся. Для CPU прошлых поколений всё ещё можно использовать контейнеризацию, но МЦСТ занимается и подготовкой паравиртуализированного ядра и сопутствующих компонентов, включая KVM, QEMU, libvirt и virt-manager. Для самих ядер был произведён редизайн микроархитектуры, что дало повышение скорости работы и новые возможности. В частности, появились новые SIMD-инструкции в дополнение к имеющимся, поддержка FMA по стандарту IEEE 754-2008 (требуется в современных стандартах C), динамическая оптимизация (касается планирования, что важно для VLIW), новый контроллер прерываний (необходим для виртуализации) и так далее. Пиковая теоретическая производительность ядра составляет 96 Гфлопс для вычислений одинарной точности и 48 Гфлопс — для двойной. Для всего CPU это 1,5 Тфлопс и 768 Гфлопс соответственно. Предварительные тесты показывают прирост производительности в 2-2,5 раза в сравнении с Эльбрус-8СВ, но надо помнить, что очень много зависит от оптимизаций со стороны компилятора. Само ядро хоть и стало сложнее, но оно всё равно проще, чем ядра современных x86-64 процессоров. Слабым местом новых чипов, на наш взгляд, является IO-блок. В состав SoC входят четыре root-комплекса PCIe 3.0, которые в сумме дают 32 линии. Из них 8 или 16 линий можно выделить на подключение внешнего южного моста, если не хватает того, что встроен в сам чип. Он предоставляет 2 порта SATA 3.0, 4 порта USB 3.0/2.0 и два мульти-порта, дающих или пару SATA, или пару Ethernet с максимальной конфигурацией 10GbE + 2.5GbE. Ещё 8 линий PCIe можно отдать на канал для межпроцессорной связи (IPL) в дополнение к двумя каналам, которые есть всегда. В двухсокетной системе, таким образом, можно объединить CPU двумя или тремя IPL. Правда, скорость одного такого канала составляет всего 12 Гбит/с (на инженерных образцах пока достигли 10 Гбит/с), что значительно меньше, чему у UPI или Infinity Fabric. Всего в одной системе может быть объединение до четырёх процессоров. Помимо прочего, в чипах реализованы различные RAS-функции для повышения надёжности работы. Также улучшен мониторинг процессора и управление его питанием и охлаждением. Вероятно, теперь уже все системы на базе новых CPU будут комплектоваться BMC-контроллером — ASPEED AST2500 и в перспективе AST2600 — с собственной прошивкой на базе OpenBMC и с встроенной микро-ОС, упрощающей инициализацию и работу с оборудованием. Референсный дизайн двухсокетной платы 2Э16С-SPRC появится в середине этого года, а однопроцессорной Micro-ATX — к концу. В 2022 году появятся и другие варианты двух- и четырёхсокетных систем с Эльбрус-16С, а также одно- и двухсокетные платы для Эльбрус-12С. Партнёры МЦСТ, надо полагать, тоже не будут сидеть без дела. Напомним, что формально окончание разработки Эльбрус-16С намечено на конец этого года. Для Эльбрус-2С3 и Эльбрус-12С точные сроки озвучены не были. И если 12-ядерная модель, скорее всего, очень похожа на 16-ядерную, то младший чип серии заметно от них отличается. Эльбрус-2С3 имеет всего два ядра шестого поколения с тактовой частотой 2 ГГц, два канала памяти DDR4-3200 и производительность до 192/96 Гфлопс FP32/FP64. У него есть 16 линий PCIe 3.0. В его состав входит 3D-ядро Imagination PowerVR GX6650 (300 Гфлопс), ряд (де)кодеров видео, а также 2D-ядро собственной разработки. Есть четыре видеовыхода (из них 2 HDMI) и поддержка 4K-вывода. Для этой SoC компанией в течение 2021 года будут подготовлены первые платы Micro-ATX и Mini-ITX. Характеристики будущих процессоров Эльбрус-32С пока до конца не определены, но примерные очертания будущего продукта уже есть. CPU должен иметь производительность не ниже 1,5/3/6 Тфлопс для вычислений FP64/FP32/FP16 и содержать от 32 ядер с частотой более 2 ГГц. Возможно, будет и 64 ядра седьмого поколения E2K. Объём L3-кеша должен как минимум удвоиться, а контроллер памяти, возможно, получит поддержку DDR5 объёмом не менее 4 Тбайт/сокет. Предполагается возможность работы как минимум двухсокетных конфигураций. Дальнейшее развитие могут получить виртуализация и фирменная технология безопасных вычислений с попутным добавлением новых инструкций. Уже сейчас разработчики хотят предоставить 64 линии PCIe 5.0, что открывает путь к использованию CXL 2.0. К встроенным контроллерам, помимо NVMe, без которого уже точно не обойтись, могут добавиться 100GbE и USB 3.1 или более новые. Будущие кристаллы перейдут на техпроцесс не толще 7 нм, а их площадь вырастет до 600 мм2. |

|